传统封装方法已无法满足人工智能、高性能计算和下一代通信技术的需求。晶体管尺寸已缩小至个位数纳米量级,但传统印刷线路板技术仍局限于20到30微米的线宽。这种三个数量级的差距造成了根本性瓶颈,Interposer和基板必须通过全新的设计和制造方法来解决这一问题。

2025-08-22 16:25

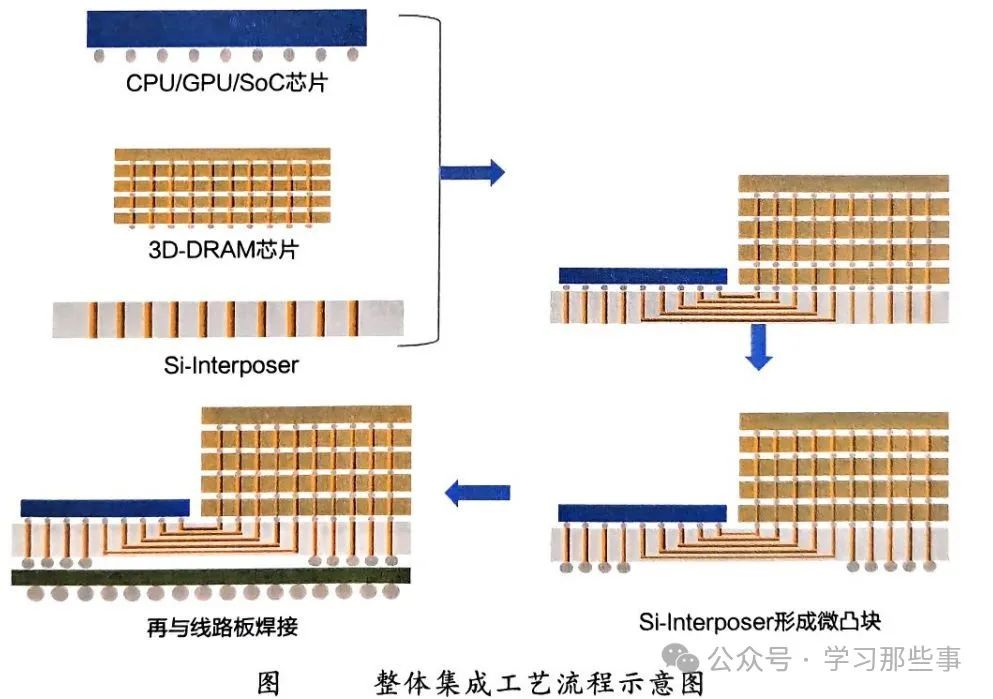

原创 StrivingJallan 芯片SIPI设计 为了克服硅中间层技术的尺寸限制,并实现更好的处理器和存储器集成,开发了一种基于硅interposer的新型2.5D SiP,如图所示。多个芯片

2024-12-10 10:38

这篇文章简要介绍CEA-Leti发布用于Chiplet 3D系统的硅光Interposer工艺架构,包括硅光前端工艺 (FEOL)、TSV middle工艺、后端工艺 (BEOL) 和背面工艺。

2023-08-02 10:59

Interposer封装作为当前主流的先进封装技术,实现的重点主要在于轻薄小巧、高速信号、密度和间距缩微三大方面,对PCB的布线密度,信号完整性,可靠性等提出了极为严苛的要求。

2022-02-09 14:21

裸芯通过微凸点组装到Interposer上,如上图所示。其Interposer上堆叠了三颗裸芯。Interposer包括两种类型的互联:①由微凸点和Interposer

2023-04-10 11:28

此外,智原对于Interposer的需求会进行芯片大小、TSV、微凸块间距和数量、电路布局规划、基板、功率分析和热仿真等信息研究,深入了解Chiplets信息并评估Interposer制造及封装的可执行性。

2023-09-12 16:27

2.5D封装工艺是一种先进的半导体封装技术,它通过中介层(Interposer)将多个功能芯片在垂直方向上连接起来,从而减小封装尺寸面积,减少芯片纵向间互连的距离,并提高芯片的电气性能指标。这种工艺

2025-02-08 11:40

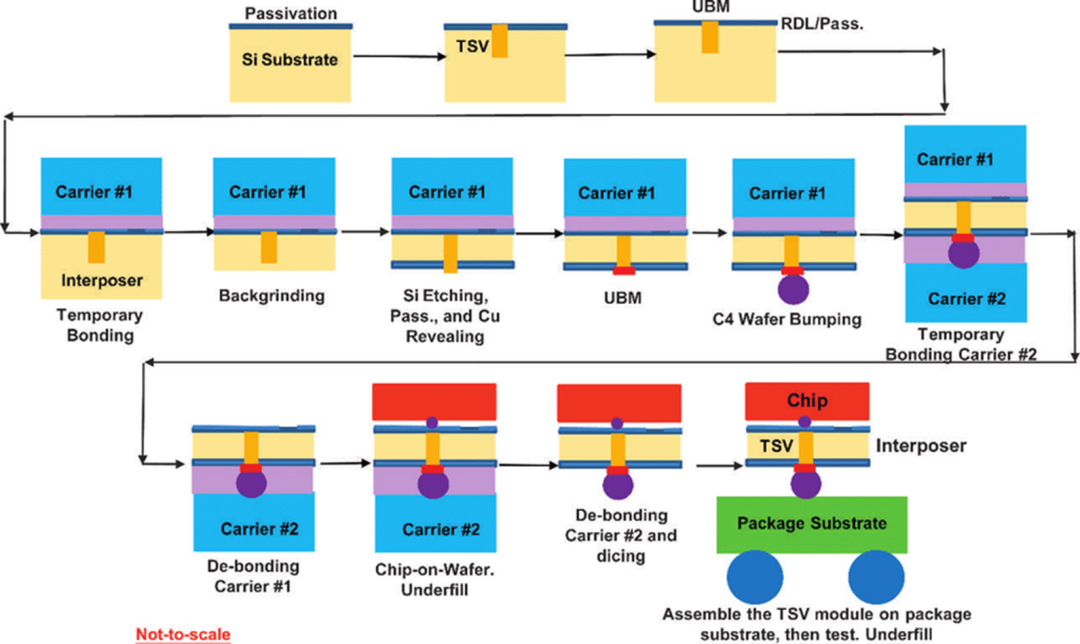

CoWoS(Chip-on-Wafer-on-Substrate),指的是将多个裸片(die)集成在一个TSV转换板(interposer)上,然后将这个interposer连接到一个基板上。CoWoS是一种先进的3D-IC封装技术,用于高性能和高密度集成的系统级

2024-10-18 14:41

移动电话技术变革,AP+内存堆栈技术运动,Interposer第一处理芯片

2022-11-30 11:26

本次视频将为各位带来芯和的先进封装建模仿真平台Metis,我们将以一个基于cowos工艺的2.5D interposer为例,为您一步步展示GDS和IRCX文件导入,3D模型生成和切割,仿真端口

2021-12-17 17:13