ILA Cross Triggering功能使得ILA核心之间、以及ILA核心与处理器(例如,AMD Zynq 7000 SoC)之间可以进行Cross Trigger。这个功能在你需要在不同时钟域的两个

2023-11-30 10:17

ILA应该是调试AMD-Xilinx FPGA最常用的IP。

2024-05-01 10:43

其实这儿便很简单了,可以直接在画布上添加一个ILA核,再把想要的信号线连进来就行了呀,都不需要在代码里定义这个ILA核。不过这样做就说明你还没能灵活的使用Xilinx的在线调试工具了,因为还有更简单的办法哈哈。

2018-11-14 10:47

在硬件调试时,经常需要用 ILA 采集一些 FPGA 内部或者对外的初始化信号,然而在下载完 Bitstream 后立即采集这些变化稍纵即逝的信号,比如在 1uS 内手动触发 ILA 采集信号,以

2024-02-23 09:45

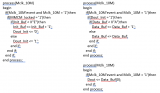

PL部分调试,作为PL DMA的控制APB总线,将其设置为Mark Debug,如下图所示。综合完成,不进行implemention,在综合菜单下面找到“Set Up Debug”,进行ILA配置。

2017-11-28 15:46

在 FPGA 开发过程中,烧写bit文件和使用ILA进行调试是再常见不过的操作。但如果 FPGA 板卡被放在机房,或者通过PCIe插在服务器上,那么每次调试时我们都不得不带着笔记本电脑跑去机房或服务器旁,接上 JTAG 线后才能进行调试,非常不便。

2025-06-05 16:41

下图红框中是ILA捕获的基本信息,可以看到捕获深度是8192,这个是我们之前设定的。主要是黄色框这个位置,它表示的是触发的位置,0表示从最初开始触发,如果你想看触发前的一些信息,就可以把它调大。比如

2018-11-16 15:18

“Sample Data Depth”是采样深度,深度越大意味着能看到的信息量越多。但是要切记一点,采样的数据都是要存储在芯片内的RAM里,所以选择越大占用的资源就越多,用户要根据自己芯片的情况选择采样深度。另外,因为使用了RAM,所以也会对布局布线产生影响,使用越多对时序可能影响越大,应该根据实际情况选择。

2018-11-13 10:32

在FPGA开发中,当我们写完代码,进行仿真,确定设计没有问题后,下载到硬件上一般都能按照我们的设计意愿执行相应功能。但这也并非绝对的,有时候你会遇到一些突然情况,比如时序问题或者仿真时我没有考虑到某种情况,但实际中它确实存在的,这就会造成功能上的错误了。

2018-06-29 05:22

FPGA设计中的信号连接到ILA核的时钟和探针输入如图1。这些信号附加到探针输入,以设计速度采样,并使用片上块RAM(BRAM)存储。核参数指定探针的数量、跟踪样本深度和每个探针输入的宽度。使用与FPGA的JTAG接口连接的自动实例化调试核心集线器与ILA核进行通

2018-08-04 10:29