随着集成电路工艺技术不断发展,为了提高集成电路的集成度,同时提升器件的工作速度和降低它的功耗,集成电路器件的特征尺寸不断按比例缩小,工作电压不断降低。为了有效抑制短沟道效应,除了源漏的结深不断降低和沟道的掺杂浓度也不断增加外,栅氧化层(Gate oxide)的厚度也在不断降低,从而提高栅电极电容,达到提高栅对沟道的控制能力,同时调节阈值电压。栅氧化层的厚度是随着栅极长度的减小而近似线性降低的,每一代大概是前一代的0.7倍左右,从而获得足够的栅控能力。另外,随着栅氧化层厚度的不断降低,MOS管的驱动能力也会相应提高。

2024-01-19 10:01

高介电常数栅电介质和金属栅极技术(以下简称HKMG)使摩尔定律在45/32纳米节点得以延续。目前的HKMG工艺有两种主流整合方案,分别是先栅极和后栅极。后栅极又称为可替换栅极(以下简称

2012-05-04 17:11

Chipworks制程分析室的研究人员对使用台积电28nm HPL制程工艺(基于gatelast HKMG技术)制作的赛灵思Kintex-7 FPGA芯片进行了工艺 解剖,这是分析报告。

2017-02-11 06:39

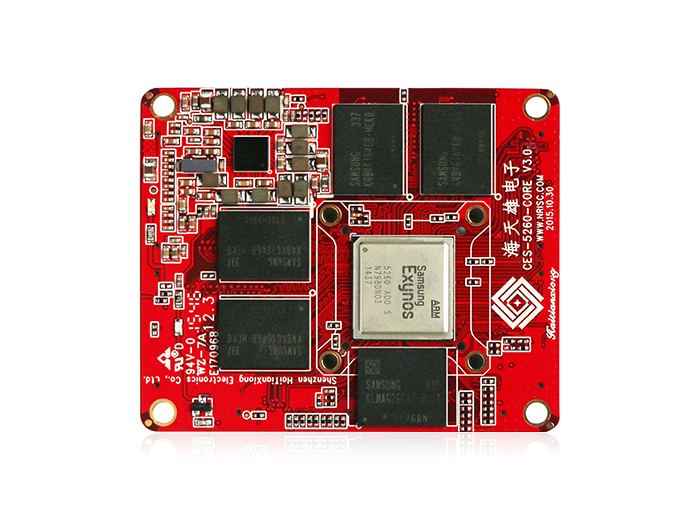

Exynos5260核心板是一款低功耗、高性能的嵌入式ARM 主板,使用Samsung高端主流ARM处理器:六核架构,双核Cortex-A15 + 四核Cortex-A7,主频最高可达1.7GHz,采用了28纳米的HKMG工艺,配备Mali-T628 MP3 GPU,性能强大。

2019-11-11 15:51