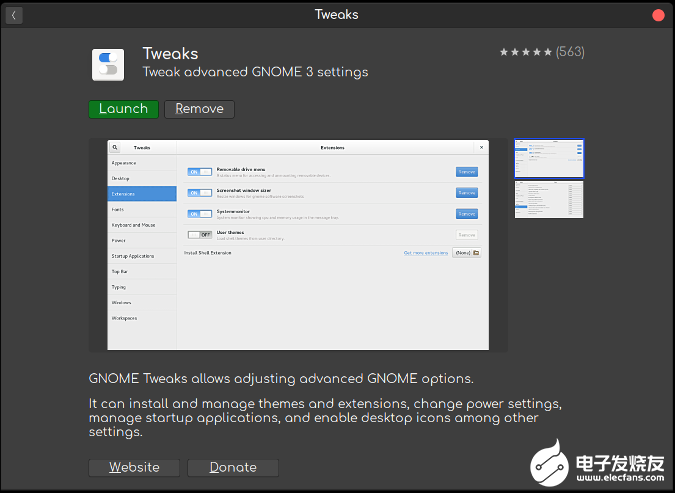

GNOME 是一个相当简单和精简的 Linux 图形用户界面(GUI),很多用户喜欢它的简约外观。虽然它基本上是开箱即用的,但你可以根据自己的喜好来定制 GNOME 。有了 GNOME “优化” 和用户主题扩展,你可

2020-09-07 11:12

有时候在debug GT的时候,需要用Digital monitor读出RX equalizer的code,本篇文章以US+的GTM为例子,提供了一个步骤,详细寄存器可以参考UG581.

2023-12-16 10:27

FP-AI-MONITOR1是一种多传感器AI数据监控框架(基于面向STM32Cube的功能包),工作于无线工业节点。针对由X-CUBE-AI(面向STM32Cube的扩展包)或NanoEdge

2022-09-29 09:04

现在的FPGA算法的实现有下面几种方法: 1. Verilog/VHDL 语言的开发 ; 2. system Generator; 3. ImpulsC 编译器实现从 C代码到 HDL 语言; 4.

2017-11-17 14:29

system generator是xilinx公司的系统级建模工具,它是扩展mathworks公司的MATLAB下面的simulink平台,添加了XILINX FPGA专用的一些模块。加速简化了FPGA的DSP系统级硬件设计。

2017-02-11 19:21

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可是设置

2017-02-11 11:53

前一阵一直在忙,所以没有来得及写博文。弄完杂七杂八的事情,又继续FPGA的研究。使用Verilog HDL语言和原理图输入来完成FPGA设计的方法都试验过了,更高级的还有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10

本文是Speos Sensor System(SSS)的使用指南,这是一个强大的解决方案,用于camera sensor模拟结果的后处理。本文的目的是通过一个例子来理解如何正确使用SSS。当然本文描述的分析步骤适合任何案例。

2023-12-03 09:49

$strobe只有在被调用时才会对其中的参数进行监测,此时的参数所具有的值可以认为是其所在当前时间槽(time-slot)中的最终值。另外,$strobe在设计中可以多次被调用,且多次调用相互之间不产生任何影响。

2024-01-22 09:38

采用System Verilog语言设计了一种具有层次化结构的可重用验证平台,该平台能够产生各种随机、定向、错误测试向量,并提供功能覆盖率计算。将验证平台在Synopsys公司的VCS仿真工具上运行

2018-01-12 11:28