Compute Express Link 是一种缓存一致性互联,旨在帮助系统(尤其是具有加速器的系统)更高效地运行。CXL位于 PCIe Gen5链路基础架构之上。可以有 PCIe Gen5 设备

2022-03-23 15:26

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

2023-06-08 15:29

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及一些特性。

2024-11-05 15:45

这款移动GPU的测试平台为桌面Z390主板+i7-9700,显卡为测试版的Gen 12 移动显卡,也就是Xe架构的GPU。这款Gen 12 移动显卡为96组CU,GPU频率最高为1.5GHz,显存为3GB。

2020-03-05 17:32

新洁能650V Gen.7系列IGBT产品,基于微沟槽场截止技术,可大幅提高器件的元胞结构密度。采用载流子存储设计、多梯度缓冲层设计、超薄漂移区设计,大幅度提升器件的电流密度。同时优化了器件的开关特性,为系统设计提供更大的余量。

2024-08-15 16:34

Rapid IO协议由于无主机,且各设备之间可以并行交换信息,所以广泛应用于对交换速率要求高,且交互复杂的应用中。Xilinx现在有支持Serial RapidIO Gen2的核,可以应用在此场景中

2018-06-29 09:02

自己的单独的 TAG。在XILINX的Virtex-7 FPGA Gen3 Integrated Block中,TAG管理相对于原来的Integrated Block for PCI Express v2.0 有一些新的特点,在使用时必须加以注意。

2017-11-18 13:16

150V Gen.3 SGT MOSFET系列产品采用全新屏蔽栅沟槽技术,特征导通电阻Rsp(导通电阻Ron*芯片面积AA)相对上一代降低43.8%,具备更高的电流密度和功率密度。同时,二极管

2024-08-15 16:36

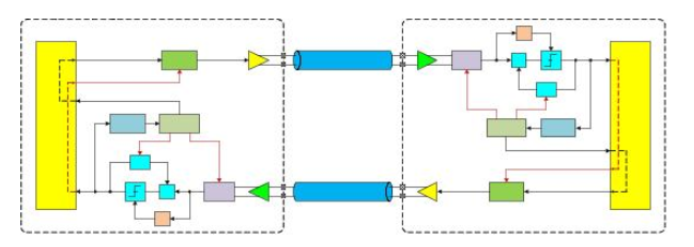

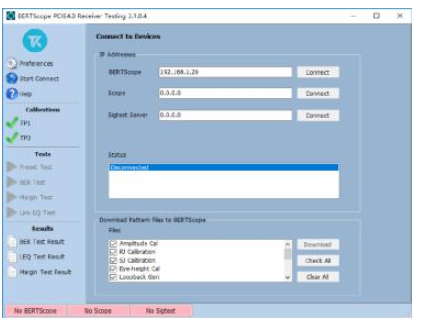

在PCIe 3.0和4.0中的链路均衡技术相较于先前代要复杂得多,这样一种动态均衡技术可以分为两个方面进行讨论。

2020-04-07 11:24

在PCIe 2.0的时代,通常只要保证了发送端的信号质量,那么整个系统也就能够正常工作;因此接收端测试并不是必测项。

2020-04-09 11:10