SOC(System on Chip,片上系统)设计中,时钟信号的控制对于整个系统的性能和功耗至关重要。本文将带您了解SOC设计中的一种时钟控制技术——Clock Gating,通过Verilog代码实例的讲解,让您对其有更深入的认识。

2024-04-28 09:12

芯片中大部分的动态功耗消耗在时钟网络中。这是由于时钟树上的单元(cells)有较高的翻转率、驱动能力较大且数量较多所导致的。

2023-12-01 14:50

画出电路、画出波形,设计意图一目了然,笔者一直推荐这种设计方案风格,画出电路图、波形图绝对是设计辅助利器。

2023-10-16 09:55

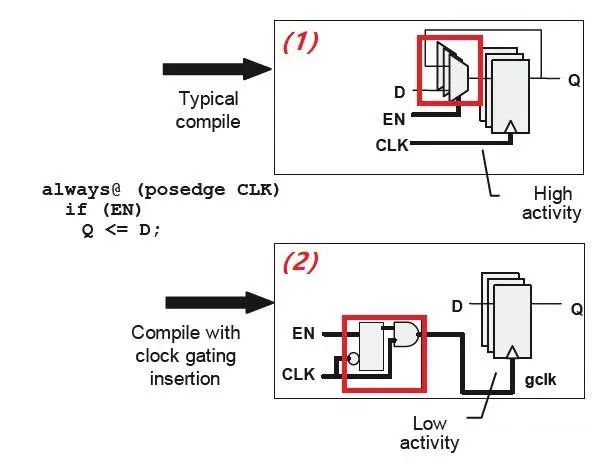

每次作为面试官问一些RTL功耗优化的问题时候,都会希望听到一个答案:优化了RTL的clk-gating比例。

2023-12-04 14:56

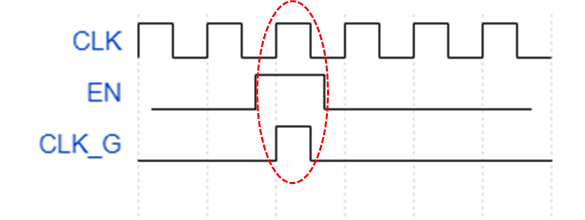

当寄存器组的输出端没有驱动或没有变化时,可以关掉寄存器组的时钟来减少动态功耗,此谓门控时钟 (Clock Gating, CG) 技术。

2023-03-29 11:37

时钟XOR自门控(Self Gating)基本思路和时钟门控类似,都是当寄存器中的数据保持不变时,通过关闭某些寄存器的时钟信号来降低设计的动态功耗。不过XOR 自门控是利用异或门(XOR)将存储在寄存器中的数据与到达寄存器的数据引脚的数据进行比较,输出门控时钟使能信号。

2024-01-02 11:34

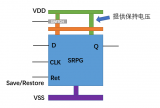

今天我们要介绍的Low Power概念是SRPG Cell,全称State Retention Power Gating Cell(状态保持电源门控单元)。这是一种特殊的寄存器,对于一般的寄存器

2018-03-16 11:12

应该是最高电压;而外设中的USB模块,有协议定义的固定速率,则只要分配给能满足要求的工作电压即可;一些平时不工作的模块甚至可以将电压关断(Power Gating),也就可使功耗趋于0。这样一个芯片中,就会划分为各种不同的电压域。

2018-01-29 10:21