当下这社会,没有几万个Clock Gating,出门都不好意思和别人打招呼!

2023-07-17 16:50

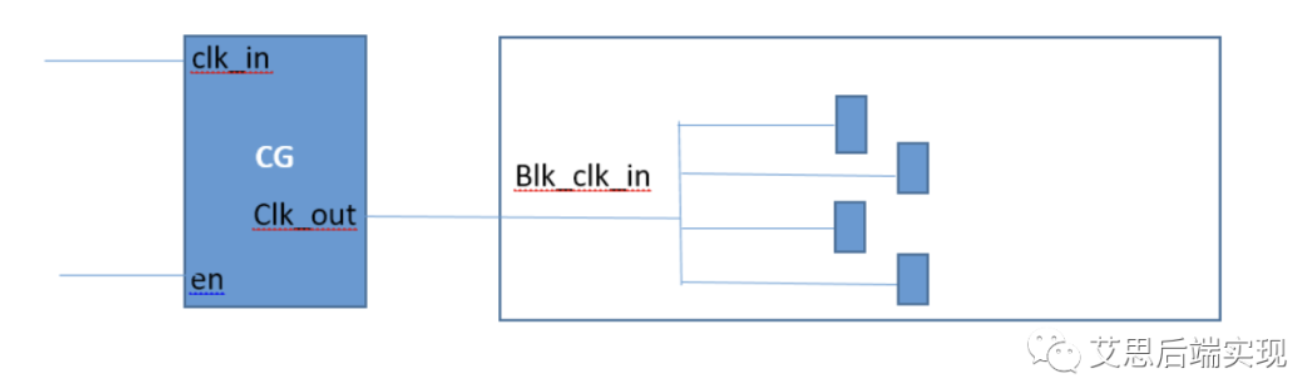

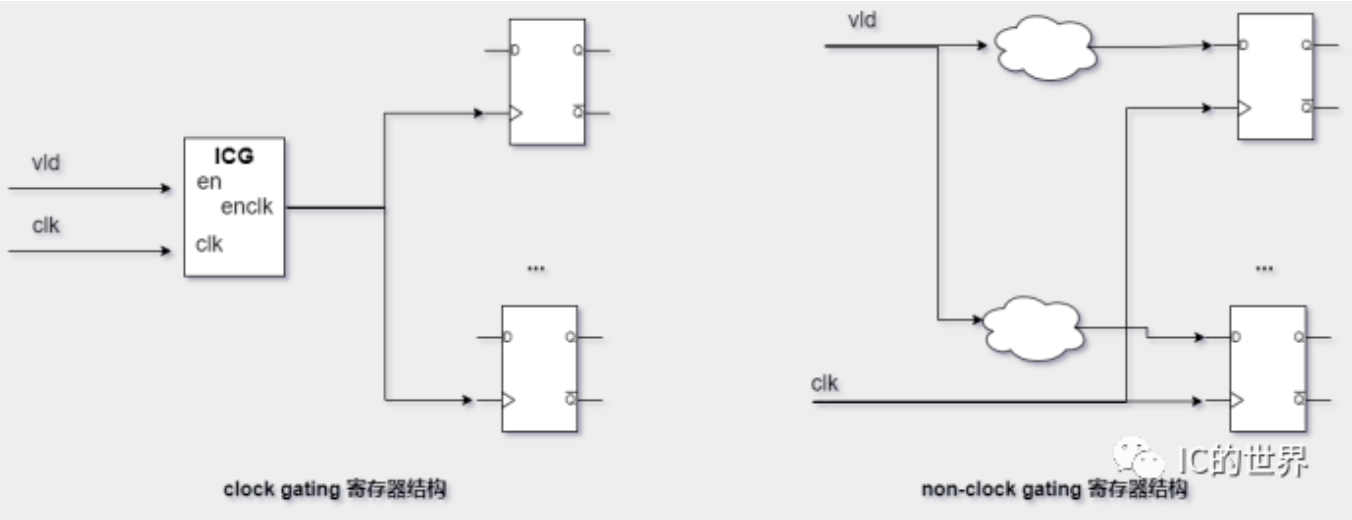

在ASIC设计中,项目会期望设计将代码写成clk-gating风格,以便于DC综合时将寄存器综合成clk-gating结构,其目的是为了降低翻转功耗。

2023-09-04 15:55

大多数低功耗设计手法在严格意义上说并不是由后端控制的,Clock Gating也不例外。

2023-06-27 15:47

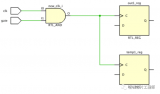

ICG(integrated latch clock gate)就是一个gating时钟的模块,通过使能信号能够关闭时钟。

2023-09-11 12:24

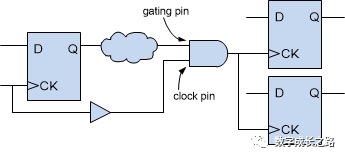

一个cell的一个输入为clock信号,另一个输入为gating信号,并且输出作为clock使用,这样的cell为gating cell。

2023-06-29 15:28

SOC(System on Chip,片上系统)设计中,时钟信号的控制对于整个系统的性能和功耗至关重要。本文将带您了解SOC设计中的一种时钟控制技术——Clock Gating,通过Verilog代码实例的讲解,让您对其有更深入的认识。

2024-04-28 09:12

首先,ASIC芯片的clock gating绝对不能采用下面结构,原因是会产生时钟毛刺

2023-08-25 09:53

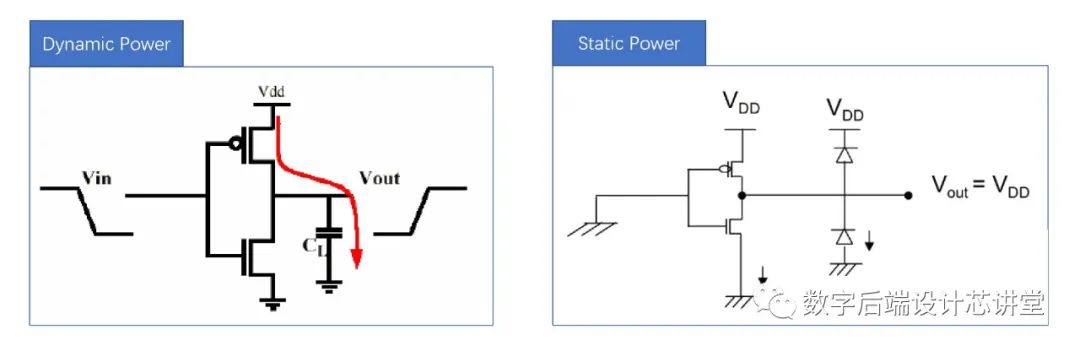

随着集成电路技术的不断发展,芯片中的晶体管数量呈现出爆炸性增长。为了提高性能,降低功耗,SoC设计中采用了各种优化技术

2023-10-07 11:39

现在的深亚纳米工艺的设计中,低功耗已经是一个日渐总要的主题了,尤其是移动市场蓬勃发展起来之后,功耗的要求越来越严格,据传,在高级的手机系统开发的过程中,系统架构的设计,已经精确到每一个服务模块的毫安时(mAH)的级别,所以如果你的芯片功耗控制不下来,很有可能会被手机生产厂家踢出局。

2023-07-14 10:14

当CK为0时,ECK 恒定为0, q值为E:如果E为1,则q为1,如果E为0,则q为0。 当CK为1时,ECK 恒定为q(n),即对应的上一次CK为0时,锁存的E值。 因此最终的效果就是,只要E配置成了0,那么ECK会在CK的下降沿跳变成0,随后只要E保持为0,那么ECK一直为0。

2023-10-16 09:43