我们的常规设计,一片液晶面板需要两种DDIC。

2023-02-02 09:21

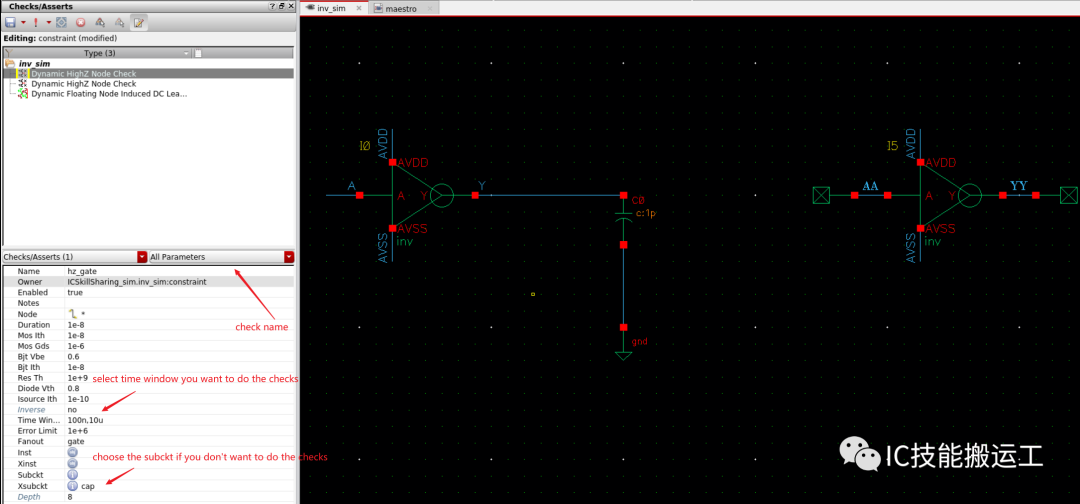

如果你还在用“笨方法”一个节点一个节点地检查电路中是否有floating的gate,那么你真的该仔细阅读一下这次的内容,并尝试在项目中使用文中介绍的方法进行floating gate检查。

2023-09-11 12:39

上一次分享的关于floating gate检查的内容有不少人反映操作步骤很多,有时候按照步骤一步步来可以把流程走通,但是抛开教程就无从下手,所以这里再次分享一个简单一点的版本,希望帮助大家完善设计流程。

2023-06-14 12:30

画出电路、画出波形,设计意图一目了然,笔者一直推荐这种设计方案风格,画出电路图、波形图绝对是设计辅助利器。

2023-10-16 09:55

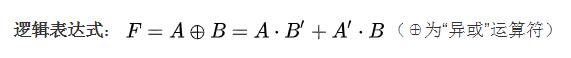

异或门 (英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、一个

2020-11-19 16:06

8253的6种工作方式:方式1:计数结束中断,GATE保持高电平,输出NxT的低电平,后变为高电平并保持不变。计数中如果GATE突然变成低电平,然后变回高电平,则延长低电平输出时间,延长时间为GATE变为低电平的时间

2019-11-15 10:33

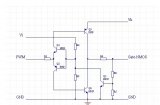

同时,如果简单的用电阻分压的原理降低gate电压,就会出现输入电压比较高的时候,MOS管工作良好,而输入电压降低的时候gate电压不足,引起导通不够彻底,从而增加功耗。

2018-04-25 15:35

FPGA(Field Programmable Gate Array)学习需要具备一系列的课程知识和实践技能

2024-03-14 15:51

当使用5V电源,这时候如果使用传统的图腾柱结构,由于三极管的be有0.7V左右的压降,导致实际最终加在gate上的电压只有4.3V。这时候,我们选用标称gate电压4.5V的MOS管就存在一定的风险。

2019-02-18 14:21

GATE为1时,定时器的计数受外部引脚输入电平的控制(INT0控制T0的运行,INT1控制T1的运行);GATE为0时定时器计数不受外部引脚输入电平的控制。

2018-11-07 16:39