。另外,用户还可以使用NI VeriStand,通过基于FPGA 的I/O接口创建用户自定义的I/O硬件。本文说明了使用基于FPGA

2017-11-18 07:47

面对似乎层出不穷的新 I/O 标准,目前嵌入式系统设计人员继续依靠 FPGA 来部署系统日益重要的外部 I/O 接口,这点丝毫不足为奇。FPGA 可提供大量可配置的

2010-11-02 09:50

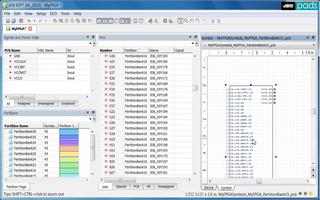

FPGA I/O 优化功能提供了自动化 FPGA 符号生成流程,该流程与原理图设计和 PCB 设计相集成,可节省大量创建 PCB 设计的时间,同时提高原理图符号的总体质量和准确性。

2019-05-20 06:16

今天给大侠带来基于FPGA的 模拟 I²C 协议设计,由于篇幅较长,分三篇。今天带来第三篇,下篇,程序的仿真与测试。话不多说,上货。

2022-08-09 15:34

本文介绍一个FPGA 开源项目:PCIE I/O控制卡。上一篇文章《FPGA优质开源项目– PCIE通信》开源了基于FPGA的PCIE通信Vivado工程,用于实现上位

2023-09-01 16:18

提出了一种基于FPGA实现的PCI-I2S音频系统方法。通过在FPGA中将PCI软核、FIFO以及设计的接口电路等相结合,在FPGA上实现了 PCI、

2017-11-17 08:17

对于需要在PCB板上使用大规模FPGA器件的设计人员来说,I/O引脚分配是必须面对的众多挑战之一。 由于众多原因,许多设计人员发表为大型FPGA器件和高级BGA封装确定I

2019-06-03 08:06

I²C 协议提供了 3 种速度模式:正常速度模式 100kbit/s、快速模式 400kbit/s、高速模式3.5Mbit/s。SCL 输出的时钟信号频率和速度模式一致。程序内部使用 5 倍 SCL 信号作为时钟,而 FPGA 外部时钟需要经过分频得到程序内部使用

2023-07-25 10:37

本文将探讨FPGA时钟分配控制方面的挑战,协助开发团队改变他们的设计方法,并针对正在考虑如何通过缩小其时钟分配网络的规模来拥有更多的FPGA I/O,或提高时钟网络性能的设计者们

2011-03-30 17:16

本文以标准的I2C 总线协议为基础,提出了一种基于FPGA的I2C SLAVE 模式总线的设计方案。方案主要介绍了SLAVE 模式的特点。给出了设计的原理框图和modelsim 下的行为仿真时序图

2014-02-26 11:39