PCIe 6.0 规范于 2021 年发布,采用 PAM4 调制(即 4 电平脉冲幅度调制),使数据传输速度翻倍,达到 64GT/s。同时,PCIe 6.0 规范使用 FLIT(流量控制单元)作为新的数据传输单元,显著提高了传输效率。

2025-02-27 15:44

PCIe 6.0还实现了PAM4 (Pulse Amplitude Modulation 4)等级的讯令,以及基于流量控制单元(flow control unit,Flit)的编码,后者支援PAM4

2022-07-07 16:56

在引入 Flit 模式后,TLP Header 中的信息进行了重新调整。除基本包头外,还可以将正交头内容 (OHC) 添加到 TLP 中。OHC 作为 TLP 的额外包头,包含 TLP 类型所需的信息字段。

2025-02-18 13:55

速率,通过x16配置可达256GB/s 四电平脉冲幅度调制(PAM4)信号,利用业界现有的PAM4 轻量型前向纠错(FEC)和循环冗余校验(CRC)可以降低与PAM4信号相关的误码率增加 基于Flit

2022-01-13 09:32

/s,使用了四级脉冲幅度调制(PAM4)信令和1b/1b flit模式编码和前向纠错(FEC),这些都延用了之前PCIe 6.0规范的功能。

2023-06-25 10:48

PCIe 7.0 接口将继续使用 1b/1b flit 模式编码和随 PCIe 6.0 引入的 PAM4 信号技术,这与PCIe 3.0 到PCIe 5.0 规范中使用的 128b/130b 编码

2022-07-28 15:11

/s,使用了四级脉冲幅度调制(PAM4)信令和1b/1b flit模式编码和前向纠错(FEC),这些都延用了之前PCIe 6.0规范的功能。

2023-06-21 11:32

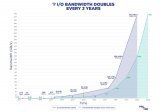

传输可变大小TLP到固定大小FLIT。 图:PCIe发展历史(来源:新思科技) PCIe 6.0的新变化 从PCIe的发展历史可以看到,在2017年以前,发展速度相

2023-01-31 09:23