DR2与DDR有哪些区别?DDR3与DDR2的区别是什么?

2021-10-26 06:15

2017-04-17 11:57

DR2

2009-11-17 13:35

图为阮新波的《全桥变换器的软开关技术》,其中“3.5 整流二极管的换流情况”,在ip不能满足副边电流后,副边的Lf强行续流,导致Dr2导通,进而导致变压器被短路。但是我有两个问题1. 此时变压器已经

2018-12-18 10:37

;***it EN1=P1^1;***it DR1=P1^2;***it CP2=P1^3;***it EN2=P1^4;***it

2015-04-27 20:40

DDR3内存与DDR2内存相似包含控制器和存储器2个部分,都采用源同步时序,即选通信号(时钟)不是独立的时钟源发送,而是由驱动芯片发送。它比DR2有更高的数据传输率,最高可达1866Mbps;DDR3还采用8位预取技

2019-06-25 15:49

DDR3内存与DDR2内存相似包含控制器和存储器2个部分,都采用源同步时序,即选通信号(时钟)不是独立的时钟源发送,而是由驱动芯片发送。它比DR2有更高的数据传输率,最高可达1866Mbps;DDR3还采用8位预取技

2019-09-18 14:27

1接收到数据后,系统会置DR1为低电平;而当接收器2接收到数据后,系统将置DR2为低电平。欲使接收器1将接收数据的字1送至16位数据总线上,应先置SEL为低电平,再置OE1为低电平且置OE

2019-06-20 05:00

、Lr、Q4向负载供电,同时给结电容C2、C3充电。 变压器副边DR1导通,DR2截止,DR1、Lf、Rd构成供电回路。 滤波电感Lf的电流在电压VLf=Vin/n-

2023-11-16 15:18

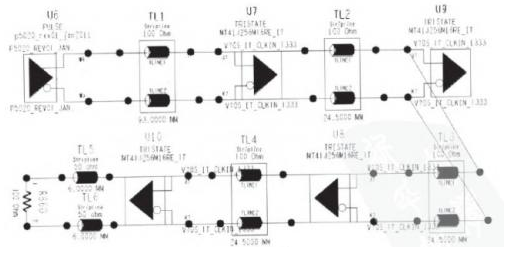

微控制器的USB口相连,实现无线数据的接收和发送。下面以接收无线数据为例。主程序U***TaskLoop,它是一个无限循环,仅仅在中断的时候跳出。程序检测nRF2401的DRl和DR2引脚,当DRl上

2019-04-08 09:36