最近接触到了一些产线的Test的东西,然后发现这里面有一些DFX的相关东西。

2023-11-05 17:04

今天分享是《DFX可制造性设计与组装技术》 资料

2023-12-11 11:10

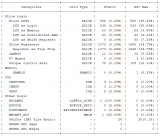

针对DFX设计,Vivado提供了命令report_pr_configuration_analysis,该命令会从设计复杂度、时钟和时序等方面对其进行分析。使用该命令时,我们主要会用到其中3个选项:-complexity、-clocking和-timing。

2023-11-09 11:23

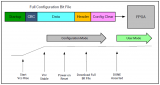

Fullconfiguration bitstreams对应的是静态区加动态区的完整设计,因此,该文件与传统的非DFX工程生成的bitstream从文件格式到文件结构均是一致的。同时使用方法也是一致

2023-12-07 10:45

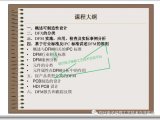

DFX是 Design for X 的缩写,是指面向产品生命周期各环节(或者某一环节)的设计。其中,X可以代表产品生命周期或其中某一环节,如装配、加工、测试、使用、维修、回收、报废等,也可以代表产品竞争力或决定产品竞争力的因素,如质量、成本(C)、时间等等。

2019-10-18 17:53

采用UltraScale/UltraScale+芯片进行DFX设计时,建议从以下角度对设计进行检查。

2024-01-18 09:27

选项-complexity聚焦在设计的资源使用情况,会给出指定RP下各RM的资源使用情况,同时给出各RM之间相比各种资源使用量的最大值,这需要用到选项-cells和-dcps。

2023-11-09 11:22

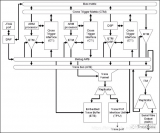

假定设计中存在两个RP,分别为RP1和RP2,那么就要避免出现RP1输出直接连接到RP2或者相反从RP2输出直接连接到RP1的路径。因为这时RP边界信号(连接RP1和RP2的net)的负载都在动态区,从而必然形成Partition Pin,由于边界信号没有经过静态区逻辑单元,这些PartitionPin最终会有相应的PPLOC,这其实就增加了后续的布线压力。这种情况下,最好将其优化为RP1->FF -> RP2。其中FF在静态区。

2023-11-30 09:17

本文介绍了在 AMD Vivado™ Design Tool 中用工程模式使用 DFX 流程以及需要注意的地方。在使用 DFX 工程模式的过程中要把具体步骤映射到相应的 DFX 非工程模式的步骤,这样才能更好地理解整

2024-04-17 09:28

DFX模式下要求在设计的顶层文件,每个RP对应的RM只以一个空的接口形式存在,这样对顶层综合时,RM就是黑盒子。而对每个RM要采用OOC的综合方式。OOC综合本质上就是工具不会对设计的输入/输出端口

2023-09-27 09:45