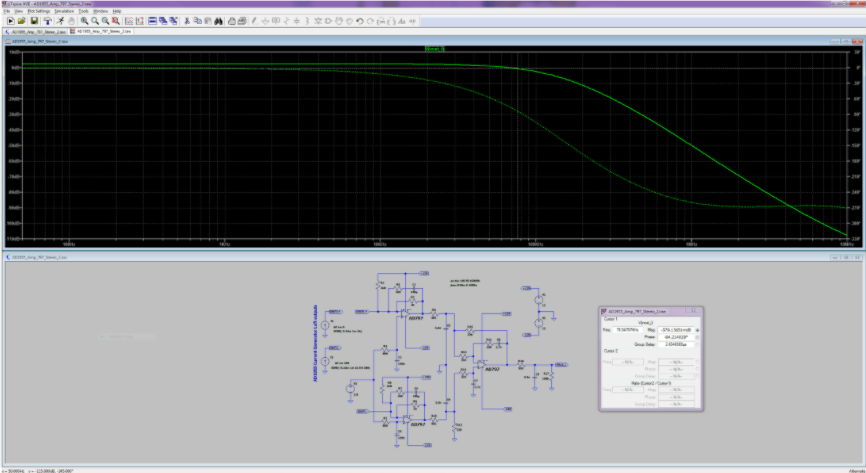

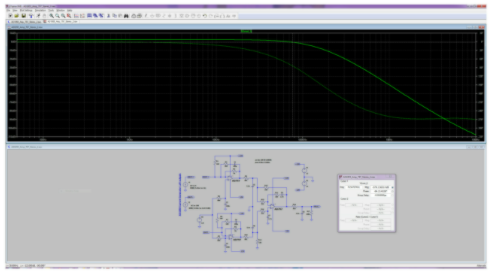

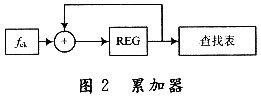

本设计在不向外扩展ROM存储器的情况下,对DDFS设计执行 优化,充分运用 Cyclone II系列FPGA的片上资源,其输出正弦信号最高频率可达4 MHz以上。只要采用更好的方案执行 设计,使采样

2017-11-24 09:32

基于CycloneII系列FPGA的DDFS信号源实现 0 引言 在电子信息领域,函数发生器(信号源)是通用的设备。近年来电子信息技术的飞速发展,使得各领域对信号源的要

2009-12-14 11:16

由于浮点运算对于需要高精度和/或高动态范围的应用至关重要,因此如今的 SHARC+ DSP 处理器,如低成本ADSP-21571或 SoC ADSP-SC571(ARM 和 SHARC)是实时处理高达 10 MSPS 的聚合采样率的事实标准。

2022-06-06 14:43

数字频率合成技术[2](Direct Digital Frequency Synthesis,DDFS)于1971年被J.Tierney首次提出。DDFS采用数字技术,以相位为出发点进行频率的合成

2018-06-22 14:55

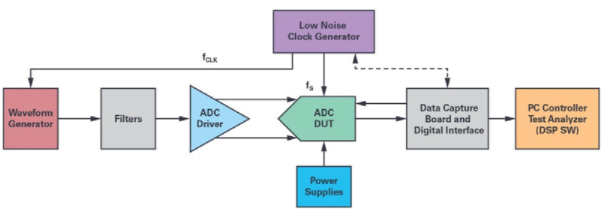

在标准评估板上进行的初步和开箱即用测试表明,基于处理器的 DDS 技术可用于具有顶级性能的传统正弦波 CW 生成。

2022-07-24 16:39

频率合成技术 (Direct Digital Frequency Synthesis,DDFS)于1971年被J.Tierney首次提出。DDFS采用数字技术,以相位为出发点进行频率的合成,具有高

2018-07-26 15:30

相位累加器寄存器的输出代表生成波形的当前相位。由于相位到正弦或相位到余弦映射器引擎,每个离散累加器输出相位值随后被转换为幅度正弦或余弦数据或样本。

2022-07-24 16:51

DDS(Direct Digital Freqiaency Synthesizers)广泛应用于雷达系统、数字通信、电子对抗、电子测量等民用军用设备中。它是随着半导体技术和数字技术的快速发展而发展起来的新型的频率合成

2010-09-29 10:40

随着微电子技术的迅速发展,直接数字频率合成器(Direct Digital Frequency Synthesis简称DDS或DDFS)得到了飞速的发展,它以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中

2012-03-30 11:38

在本系列的第1部分中,我们将了解如何设计基于直接数字频率合成(DDFS)原理的非常精确的正弦波发生器,但在浮点DSP处理器上通过软件实现。在第 2 部分中,我们将介绍如何在软件中实现高精度 NCO。

2022-11-28 17:06