电子发烧友

1.1w次浏览

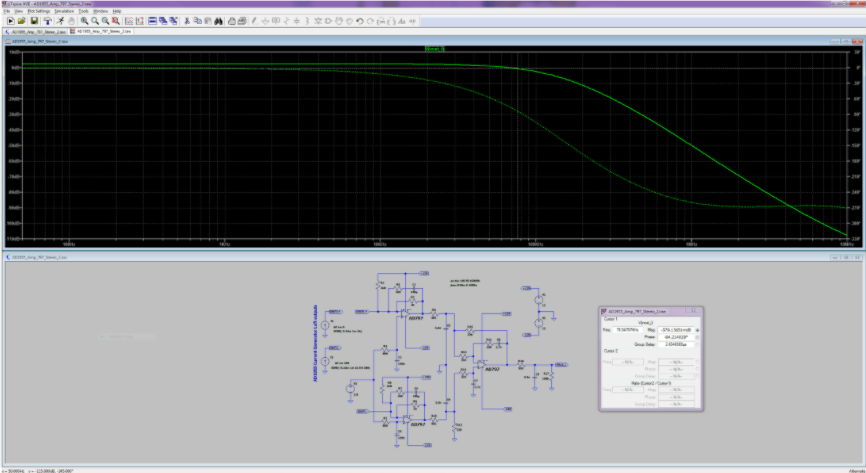

本设计在不向外扩展ROM存储器的情况下,对DDFS设计执行 优化,充分运用 Cyclone II系列FPGA的片上资源,其输出正弦信号最高频率可达4 MHz以上。只要采用更好的方案执行 设计,使采样

2017-11-24 09:32

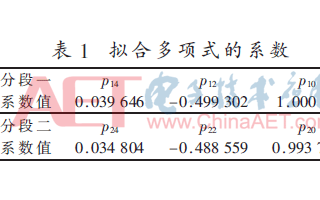

本文介绍了直接数字频率合成器(DDFS:Direct Digital Frequency Synthesizer)的基本工作原理、主要误差源及改善方法,在此基础上着重讨论了压缩数据以等效增加数据容量的Sunderland 算

2009-12-25 12:41

DDFS技术原理是什么?DDFS的FPGA实现的参数怎样去计算?如何利用FPGA去实现DDFS?

2021-04-28 07:01

,输出不同幅度的信号等。而实现频率合成要领有许多种,但基本上可以归纳为直接频率合成和间接频率合成两大类要领 。采用传统的频率合成技能要实现上述要求,几乎是不可能的。DDFS技能 是自21世纪70年代出现的一种新型的直接频率合成技能 。

2019-08-22 06:29

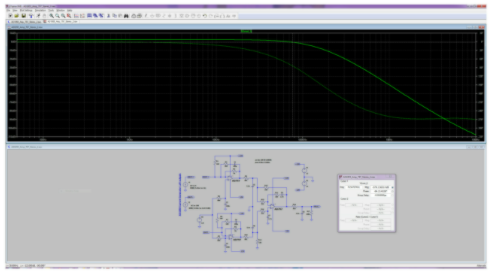

文中介绍一种基于DDFS(直接频率合成)技术的可编程音频仪器测试信号源设计。该系统采用单片机作为控制器,以FPGA(现场可编程门阵列)作为信号源的主要平台,利用DDFS技术产生一

2013-05-06 11:40

DDS的基本原理是什么,有什么性能指标?基于FPGA的DDFS与DDWS两种实现方式

2021-04-30 06:13

基于CycloneII系列FPGA的DDFS信号源实现 0 引言 在电子信息领域,函数发生器(信号源)是通用的设备。近年来电子信息技术的飞速发展,使得各领域对信号源的要

2009-12-14 11:16

由于浮点运算对于需要高精度和/或高动态范围的应用至关重要,因此如今的 SHARC+ DSP 处理器,如低成本ADSP-21571或 SoC ADSP-SC571(ARM 和 SHARC)是实时处理高达 10 MSPS 的聚合采样率的事实标准。

2022-06-06 14:43

数字频率合成技术[2](Direct Digital Frequency Synthesis,DDFS)于1971年被J.Tierney首次提出。DDFS采用数字技术,以相位为出发点进行频率的合成

2018-06-22 14:55

在标准评估板上进行的初步和开箱即用测试表明,基于处理器的 DDS 技术可用于具有顶级性能的传统正弦波 CW 生成。

2022-07-24 16:39