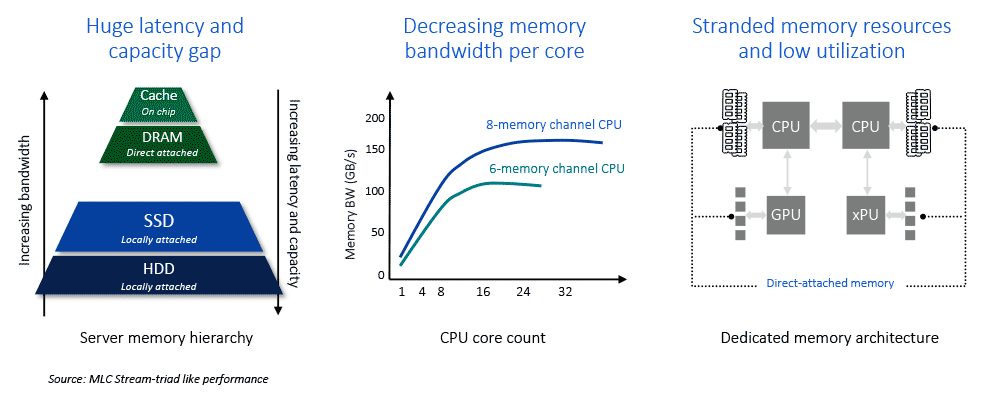

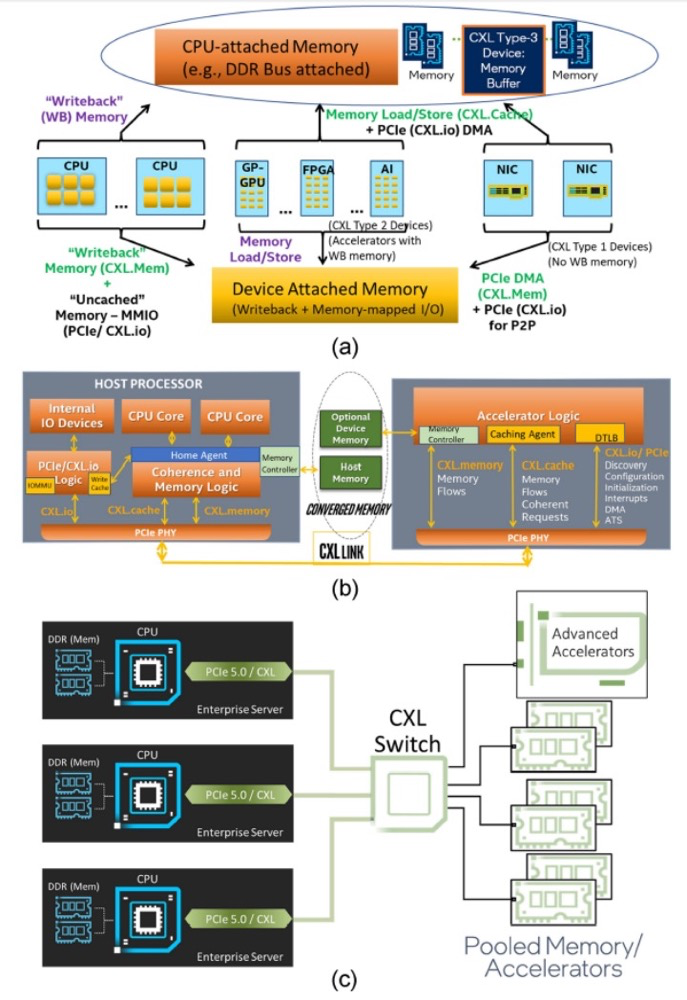

CXL的目标:解决CPU和设备、设备和设备之间的内存鸿沟。服务器有巨大的内存池和数量庞大的基于PCIe运算加速器,每个上面都有很大的内存。内存的分割已经造成巨大的浪费、不便和性能下降。CXL就是为解决这个问题而诞生。

2024-01-11 16:53

Compute Express Link(CXL)作为一种先进的互连技术,在当今高性能计算领域引起了广泛关注

2023-11-29 15:26

CXL.io为IO设备提供非一致性的load/strore接口。事务类型、事务数据包格式、信用流量控制、虚拟通道管理、事务顺序的规则等遵循PCIe协议。CXL.io的事务层如下图中的黄色部分所示。

2022-10-10 16:02

Compute Express Link(CXL)于2019年首次发布,是处理器与AI加速器、内存缓冲区、智能网络接口卡、持久性存储器和固态驱动器等设备之间的开放式行业标准互连技术。作为一种行业标准

2025-03-11 15:07

CXL 2.0 规范在 PCIe 配置空间映射寄存器中定义了多个新的 PCIe 指定供应商特定扩展功能 (DVSEC)。以下是 CXL 2.0 设备的一些强制性 DVSEC。

2023-05-25 17:22

CXL.io 和CXL.cache 是CXL 协定中的两个子协定,它们的功能和用途有所不同,主要是为了引入非对称的概念;CXL.io 类似于PCIe 的事件(event

2023-11-22 15:43

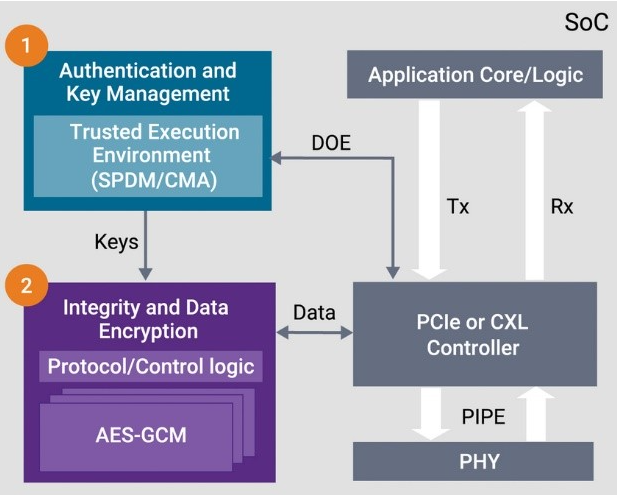

CXL 2.0规范为 CXL.io 和CXL.cache/CXL.mem协议引入了IDE原理图。CXL.io 途径使用

2023-05-25 16:41

机器学习和人工智能日益普及,虚拟机和虚拟组件上的工作负载也随之不断增加。为此,行业急需能够确定工作负载优先次序并保障性能的机制。Compute Express Link(CXL)是处理器与加速器

2024-08-02 14:43

Using Compute Express Link》(文末附链接)。在这篇文章中,Debendra Das Sharma详尽地阐述了如何利用CXL(Compute Express Link)技术

2024-09-03 09:14

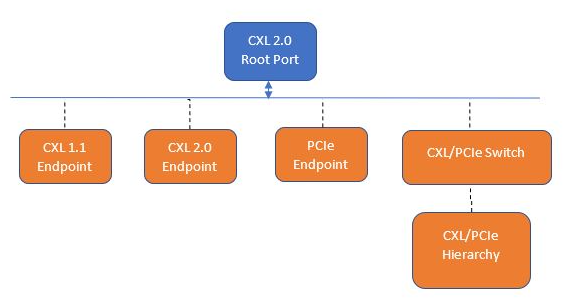

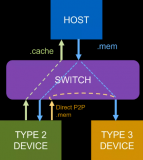

Compute Express Link 是一种缓存一致性互联,旨在帮助系统(尤其是具有加速器的系统)更高效地运行。CXL位于 PCIe Gen5链路基础架构之上。可以有 PCIe Gen5 设备

2022-03-23 15:26