现在的FPGA里面有很多存储资源,DSP(数字信号处理)资源,布线通道,I/O资源,当然最根本的还是CLB(Configurable Logic Block)。Xilinx的资源分布采用ASMBL架构。

2018-10-22 11:00

7系列FPGA是Xilinx新推出的基于28nm工艺的FPGA,其中包含三个系列:Artix、Kintex和Virtex。因项目要使用kintex7为平台做设计,需要对其内部结构做了研究,首先从CLB(Configurable Logic Block)开始

2017-02-10 16:13

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

2023-06-08 15:29

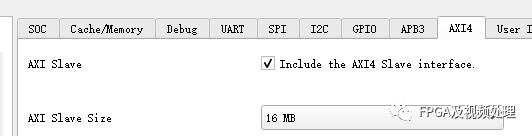

软件支持版本:目前验证了2021.2和2022.1,之前的版本应该也可以支持,需要自己验证。 打开sapphire soc,UART0和SPI0默认是勾选死的,其实也是支持去掉勾选的。下面我们来说

2022-09-01 15:24

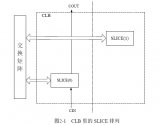

Spartan-6每个CLB模块里包含两个SLICE。CLB通过交换矩阵和外部通用逻辑阵列相连,如图2-1和图2-2所示。底部的SLICE标号为SLICE0,顶部的SLICE标号为SLICE1。两个SLICE没有直接

2017-02-11 09:53

RAID 0的组建其实比较简单.不过对于普通用户来说,在组建RAID 0之前。有不少东西还是必须得知道的,否则不能发挥出RAID0的性能

2011-01-29 18:04

0欧姆电阻即电阻标值为0欧姆的电阻,多用于PCB设计等方面,是一种理想电阻。那0欧姆电阻是表示没有电阻吗?当然不是,0欧姆电阻的阻值不是

2023-02-02 09:07

0欧姆电阻即电阻标值为0欧姆的电阻,多用于PCB设计等方面,是一种理想电阻。那0欧姆电阻是表示没有电阻吗?当然不是,0欧姆电阻的阻值不是

2022-11-01 10:59

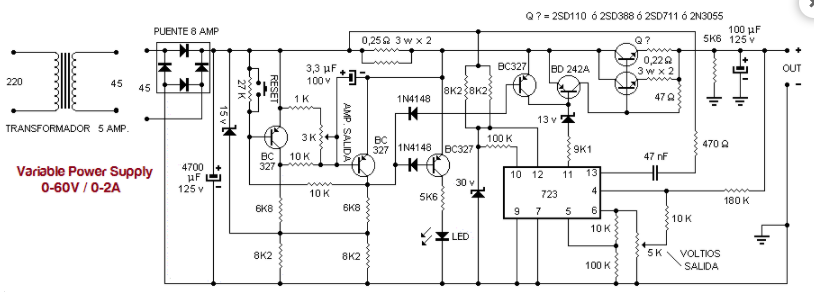

这是0-60V/0-2A可变电源的电路图。当然,该电路用于覆盖从 0 到 60V 的电压范围和从 0 到 2A 的电流。如果我们添加所需的功率晶体管,则可以增加最大电流

2022-06-21 16:33

在我们的印象中,电阻就是起到阻碍电流的作用的。但是0欧电阻?不能阻挡电流的电阻我们要它干什么用?实际上,0欧电阻并不是一开始就出现的,而且大部分0欧电阻——都是贴片电阻。这是和它的用途息息相关的。

2020-09-03 11:53