在高速串行通信中,CDR(Clock-Data-Recovery)时钟与数据恢复功能起着关键作用。CDR电路可以从数据流中同时提取出数据和时钟,链路上不再需要伴随信号发送随路时钟,大量节省IO资源

2025-09-30 17:35

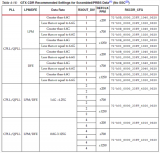

我们知道,对于PI-base CDR(XILINX 的5、6、7系列SERDES的CDR采用的共同架构),CDR的不同配置,代表作不同的CDR带宽、所能处理数据PPM偏

2017-02-10 18:38

ONET1131EC:集成 CDR 功能的外部调制激光器驱动器深度解析 在高速光通信领域,对于高性能外部调制激光器驱动器的需求日益增长。ONET1131EC 作为一款集成时钟和数据恢复(CDR)功能

2025-12-19 10:10

我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及性能数据,提出对参考时钟的相位噪声的具体要求。

2017-02-10 18:40

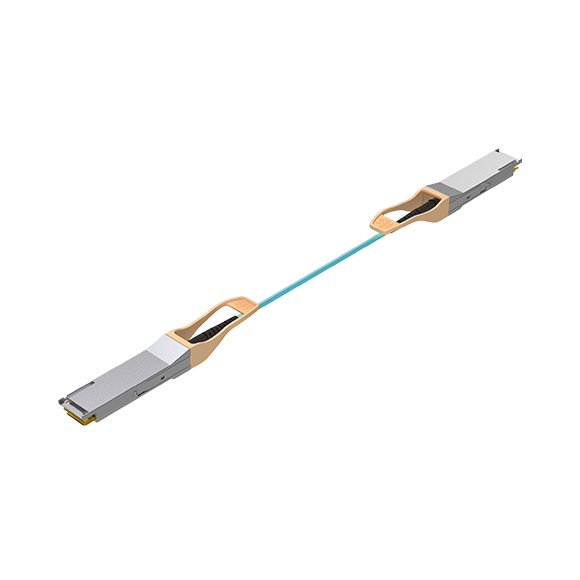

特征 4通道全双工接收模块 4通道,每通道传输数据速率28 Gbps,4通道PIN ROSA接收 接收通道内置CDR电路 低功耗< 1.5 w 热插拔QSFP封装

2019-10-11 10:48

•支持25Gb / s的聚合比特率 •850nm VCSEL •PIN光电探测器 •接收器和发送器通道上的内部CDR电路 •每端最大功耗1W •OM3 MMF的最大链路长度为70米,OM4 MMF的最大链路长度为100米

2019-10-31 09:15

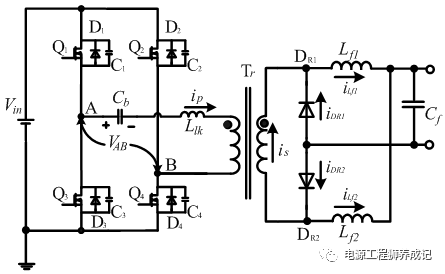

倍流整流方式( Current Doubler Rectifier , CDR) ZVS 全桥变换器利用两个输出滤波电感的能量可以在很宽的负载范围内实现开关管的ZVS而且使其输出整流管自然换流

2023-12-04 17:10

本文讨论从GSM到OC-192及更高版本的高速串行通信的时钟数据恢复(CRD)。它解释了如何通过典型链接转换和重新捕获数据。本文还研究了不同的CDR方案以及参考振荡器在通信链路发射端和接收端的作用。

2023-06-10 14:49

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号。由于时钟数据在同一个通道传播,串行信号对和对之间在PCB上传输延时要求较低,主要依靠锁相环(PLL)和芯片的时钟数据恢复功能。

2019-09-20 14:12

串行解串器 (Serializer/Deserializer, SerDes)的特点为数据与时钟在同一信道中传输,在接收端通过时钟数据恢复技术(CDR)提取数据中所包含的时钟信息并以此时钟采样接收到的数据。当前,绝大部分高速信号传输使用SerDes 结构。

2023-12-26 09:43