高度隔离的2:1 RF开关和片内可调谐RF巴伦使ADRF6820支持两个单端50 ?端接RF输入。可编程衰减器确保高线性度解调器内核具有较佳的差分RF输入电平。

2022-11-14 16:32

ADRF6820是一款高度集成的解调器和频率合成器,非常适合用于高级通信系统。 它内置一个宽带I/Q解调器、一个小数N/整数N分频锁相环(PLL)以及一个低相位噪声多核压控振荡器(VCO)。

2018-06-26 17:00

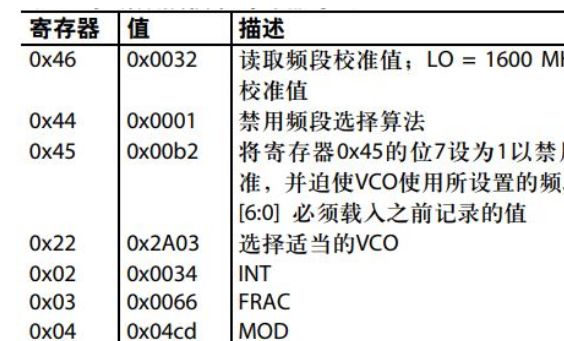

本文以高度集成的解调器和频率合成器 ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。

2020-09-01 11:34

本文以高度集成的解调器和频率合成器 ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。

2018-05-22 09:00

Analog近日发布最新高度集成式RF IC,可大幅简化多频段基站和点对点(PtP)无线电的设计并降低开发成本。这些最新器件包括:I/Q调制器ADRF6720、I/Q解调器ADRF6820和双通道混频器ADRF661

2014-06-09 11:04

ADRF6820是一款高度集成的解调器和频率合成器,非常适合用于高级通信系统。 它内置一个宽带I/Q解调器、一个小数N/整数N分频锁相环(PLL)以及一个低相位噪声多核压控振荡器(VCO)。

2022-08-09 11:23

随着越来越多的构建模块被添加到射频集成电路(RFIC)中,出现了更多的噪声耦合源,这使得电源管理变得越来越重要。本文介绍电源噪声如何影响RFIC的性能。以集成锁相环(PLL)和压控振荡器(VCO)的正交解调器ADRF6820为例,但结果广泛适用于其他高性能RFIC。

2023-02-01 16:33

随着射频集成电路(RFIC)中集成的元件不断增多,噪声耦合源也日益增多,使电源管理变得越来越重要。本文将描述电源噪声可能对RFIC 性能造成的影响。虽然本文的例子是集成锁相环(PLL)和电压控制振荡器(VCO)的ADRF6820 正交解调器,但所得结果也适用于其他高性能RFIC。

2022-11-10 11:32

随着射频集成电路(RFIC)中集成的元件不断增多,噪声耦合源也日益增多,使电源管理变得越来越重要。本文将描述电源噪声可能对RFIC性能造成的影响。虽然本文的例子是集成锁相环(PLL)和电压控制振荡器(VCO)的ADRF6820正交解调器,但所得结果也适用于其他高性能RFIC。

2015-10-26 15:32

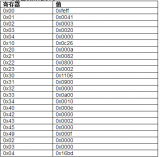

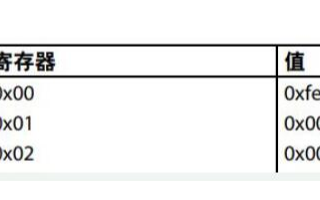

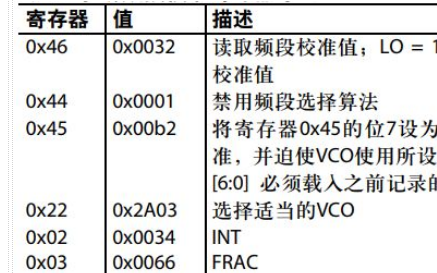

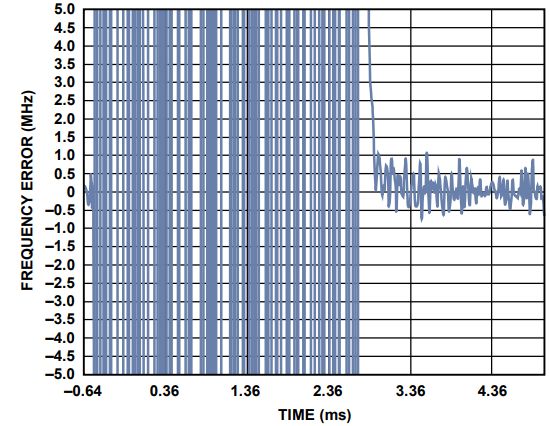

利用手动频段选择,锁定时间可从典型值 4.5 ms 缩短到典型值 360 s。 本文以高度集成的解调器和频率合成器 ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。 PLL

2018-06-13 09:33