本文来自AMD Xilinx实习生Shaoyi Chen及其同学Leslie Xu, 本教程将使用ZCU102开发板运行xdpdma例程,程序可以在显示器上显示默认画面,并总结了使用该例程时经常遇到的问题。

2022-08-03 10:27

Zynq UltraScale+ MPSoC ZCU102 评估套件使用 MAX15301 及 MAX15303 PMBus 稳压器以及 MAX20751E 主控基于 Maxim PMBus 的电源

2018-07-04 14:19

DisplayPort 1.4 Tx Subsystem core的最简pipeline就是如它的linux driver wiki page里的figure-4那样,framebuffer_read+DP+video_phy。

2023-12-29 10:09

本文依据 Vivado 2022.1 版本工具链的特性,对 UG1209( 最新版本为 2020.1 )中介绍的 USB BOOT 启动步骤做了修改,此外,介绍了 WINDOWS 10 中 DFU 工具的使用。

2022-10-28 09:50

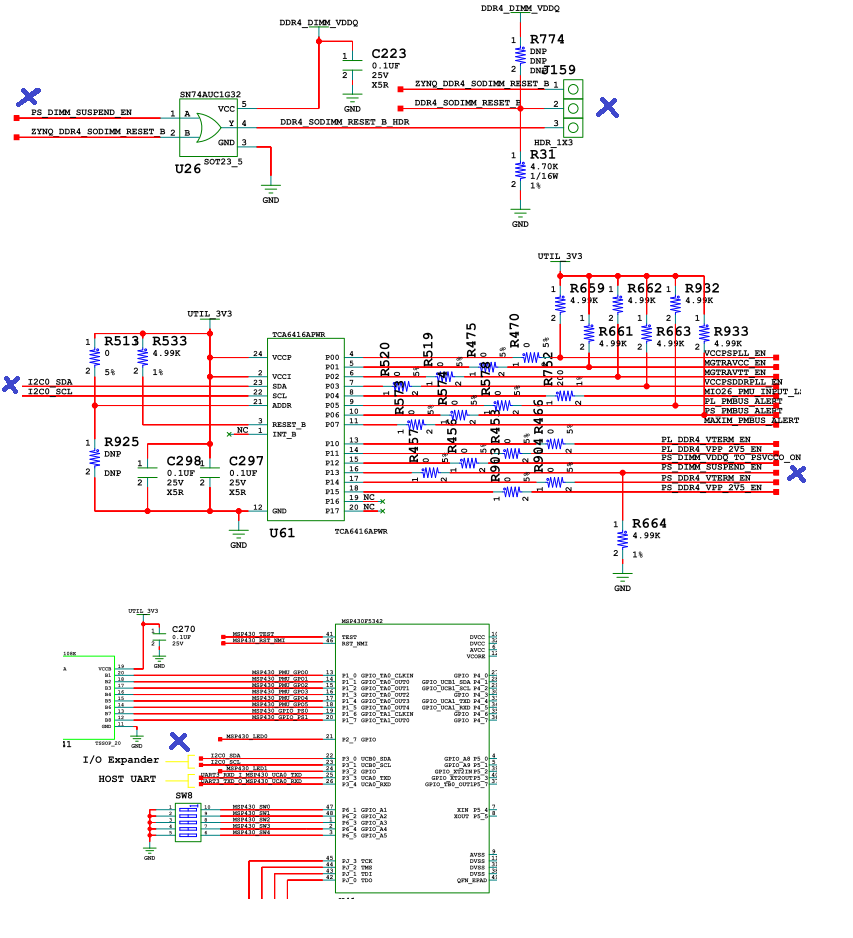

Xilinx的开发板ZCU102支持休眠到内存(suspend-to-ram)。休眠到内存时,DDR进入自刷新,MPSoC被关电,完全不耗电。唤醒时,MPSoC根据外部输入信号判断出不是上电启动而是

2020-11-04 17:02

基于vivado2020.1和zcu102开发板(rev1.1)开发项目,工程涉及DDR4(MIG)和PL端多个读写接口交互的问题,通过AXI interconnect进行互联和仲裁(采用默认配置)。

2023-12-01 09:04

本文介绍如何使能 Linux 网络协议栈中的 RFS(receive flow steering)功能以优化 MPSoC APU 的并行处理能力,解决丢包问题。 问题描述: 在测试 ZCU102

2023-06-17 08:59

本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式评估板上实现多个 UIO,同时借助赛灵思的工具完成硬件工程和 linux BSP 的开发,最后通过测试应用程序完成测试。

2018-03-21 14:55

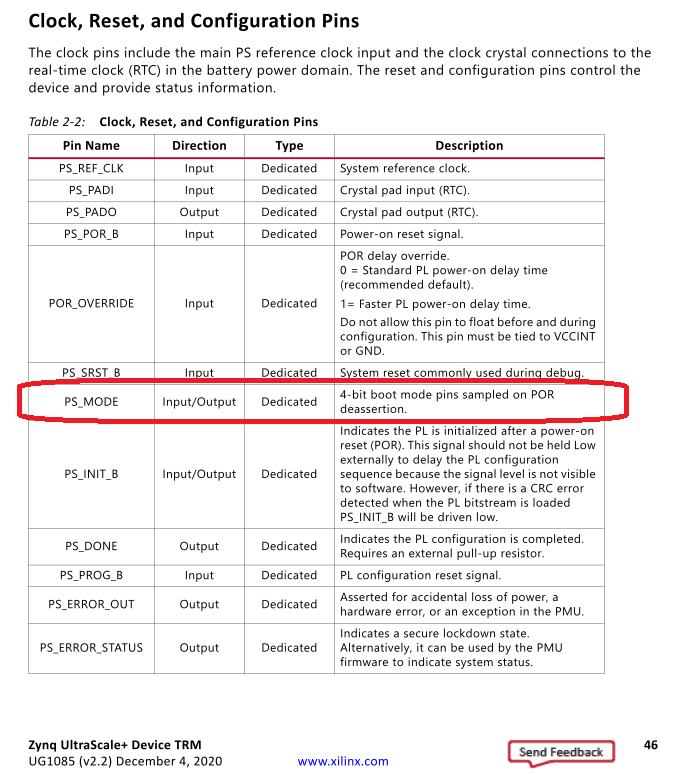

在Xilinx的ZCU102和ZCU106单板设计中,使用了管脚PS_MODE1作为外部USB Phy的复位信号。在MPSoC的文档ug1085和ug1087中,关于PS_MODE1的信息比较少。下面是更详细的描述。

2022-08-02 09:38

基于vivado2020.1和zcu102开发板(rev1.1)开发项目,工程涉及DDR4(MIG)和PL端多个读写接口交互的问题,通过AXI interconnect进行互联和仲裁(采用默认配置)。一个完整控制周期内(约100ms),各端口读写情况如下(AWSIZE均为4)。

2022-06-15 11:59