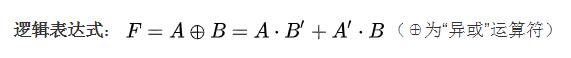

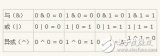

异或门是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、1个输出端,多输入异或门可由2输入异或门构成。若两个输入的电平相异,则输出为高电平1;

2017-11-28 12:07

时钟XOR自门控(Self Gating)基本思路和时钟门控类似,都是当寄存器中的数据保持不变时,通过关闭某些寄存器的时钟信号来降低设计的动态功耗。不过XOR 自门控是利用异或门(

2024-01-02 11:34

异或门 (英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、一个输出端,多输入异或门可由两输入

2020-11-19 16:06

3XOR 逻辑元件的类似物,图 5和图 6,比以前的要复杂得多,但值得考虑的是,由于执行的复杂性增加或出于其他原因,这种微电路形式的元件没有生产。 表 1(真值表)根据输入信号集表征 3XOR 逻辑元件的输出信号电平。

2023-06-05 14:19

异或门可以用于实现二进制数的加减法。例如,我们可以使用异或门来实现两个二进制数的加法,如果两个相应的输入端上输入的数相同时则进行减法运算。

2024-02-04 14:47

首先,有关XOR逻辑运算的一些基本信息:如果XOR逻辑运算的两个输入都不相同,则返回true;如果两个输入相同,则返回false。因此,true和false的输入将返回true,false和false或true和true的输入将返回false。听起来很简单,不是吗

2021-04-26 14:10

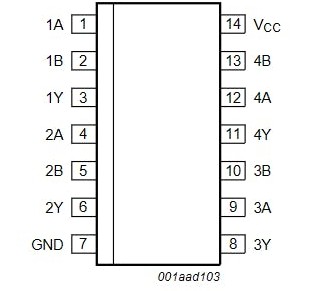

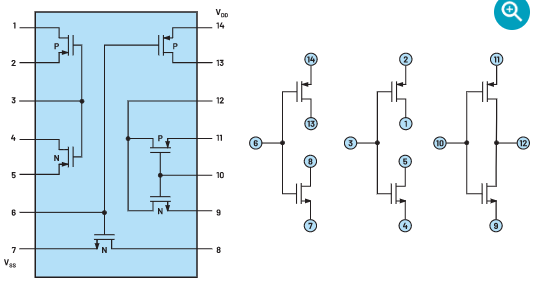

本实验活动的目标是进一步强化上一个实验活动 “使用CD4007阵列构建CMOS逻辑功能” 中探讨的CMOS逻辑基本原理,并获取更多使用复杂CMOS门级电路的经验。具体而言,您将了解如何使用CMOS传输门和CMOS反相器来构建传输门异或(XOR)和异或非逻辑功能。

2023-05-29 14:17

异或,是一个数学运算符,英文为exclusive OR,缩写为xor,应用于逻辑运算。异或的数学符号为“⊕”,计算机符号为“xor”。

2017-11-28 11:19

逻辑加法运算规则如下: 0+0=0, 0∨0=0 0+1=1, 0∨1=1 1+0=1, 1∨0=1 1+1=1, 1∨1=1 从上式可见,逻辑加法有“或”的意义。

2016-07-25 18:26

与异或门一样,也只有两个输入端,同或门输出端的小圆圈说明输出结果跟异或门输出相反,当输入的两个电平为相反电平时,同或门输出低电平。

2024-02-04 14:08