每个DEMO以文件夹为单位,从入门到进阶,根据文件夹编号为准,逐步递进。 成文时,webpack版本是【3.8.1】 0.1、安装webpack 首先你需要安装Node.js,点击打开Node.js

2017-11-29 09:10

对于现阶段而言,浏览器只识别es5,而无法识别es6,简单的说,es6代码在浏览器里会报错。 这是在webpack压缩文件时,出现未转化的es6语法,导致报错。 简单的解决办法: 找到错误点,例如

2018-01-17 01:45

Vivado HL WebPACK:文件更小且许可证正在免费! 使用 Web 安装程序安装 HL WebPACK,下载时间缩短达 2/3,下载量降低达 6GB。 而且 HL WebPACK 现在不再

2017-02-08 12:09

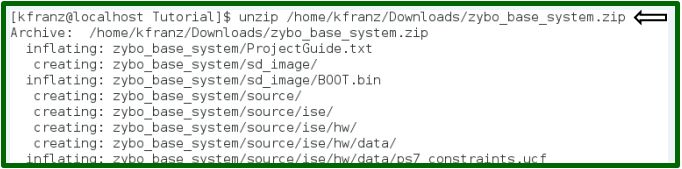

将SD卡插入ZYBO。使用insmod命令将驱动程序模块安装到内核中。运行led_blink,LED会开始闪烁。

2019-11-14 11:24

随着Vivado设计套件2012.4版的发布,客户现可立即免费下载业界首款强大的SoC级的设计工具,支持All Programmable设计。

2012-12-21 13:46

此外,根据 Turbopack 的官方解释,它基于一个用 Rust 编写的增量计算引擎 Turbo,Turbo 可实现细分到函数粒度的结果缓存、支持内存缓存,未来还将有持久化缓存和远程缓存,以及支持按需编译,尽量减少计算量。

2022-11-02 13:01

许多信号处理应用都需要进行上采样。从概念上讲,对数据向量进行M倍上采样的最简单方法是用实际频率分量数的(M-1)倍个零填充数据向量的离散傅里叶变换(DFT)[1],然后将零填充向量转换回时域[1,2]。但这种方法计算量很大,因此不能在FPGA内部高效实现。在本文介绍的高效并行实时上采样电路中,每个ADC时钟可产生M个上采样值,其中M是所需的上采样倍数。在我们赛灵思的Virtex®-6 XC6VLX75T FPGA实现方案中,上采样倍数M为4,可以作为较普遍方法的一个实例。

2017-11-18 01:22

新的器件支持包括:Kintex®UltraScale+™,Zynq®UltraScale+ MPSoC和所有Vivado HLx版本的单核Zynq-7000S All Programmable SoC器件,包括WebPACK™,基于IEEE 17350的IP加密的公共访问支持。

2018-11-20 06:50

欢迎了解我们低端系列中重要的产品系列 Spartan-6 FPGA 如何与 Xilinx ISE 设计套件 v14.7 及 ISE WebPACK v14.7 免费工具配合使用,帮助您为您的设计实现最大限度的功耗降低 以及 最佳的生产力和性能。

2019-08-01 15:23

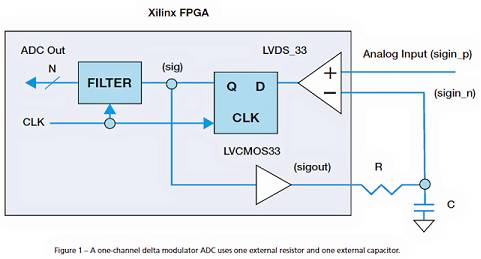

信号 sigout 是串行比特流,其经过过滤,可生成 N 位 ADC 输出。我们使用免费的赛灵思 ISE Webpack 工具实现了该项目。图 5 是 VHDL 代码以及一部分与图 1 电路系统有关的 UCF 文件。

2019-08-01 14:52