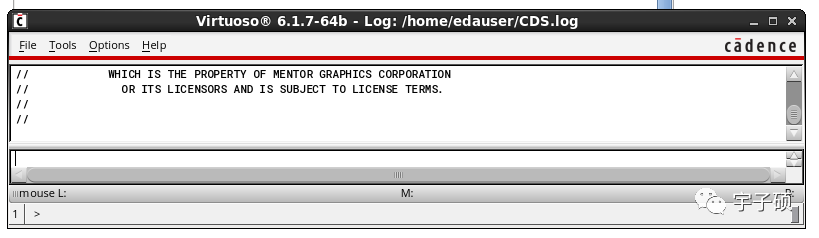

首先,在相应终端下键入virtuoso,启动后出现以下窗口。

2023-10-18 15:47

如果要想知道某变量为不同值的dc工作点,接着→Sweep Variable → select Design Variable → Variable Name选择某个变量→ Sweep Range输入温度范围

2024-01-08 14:42

如果要想知道不同温度下的dc工作点,接着→Sweep Variable → select Temperature → Sweep Range输入温度范围

2024-02-18 18:20

考虑用balun的单端转差分的功能来实现,但感觉非常不中用。要生成的差分信号带有直流偏置,结果ideal_balun只能是2:1的变化比,而ideal_balun好xfmr都有的问题是,它们都会把直流一起变化了。直流偏置也反相,那输出端口出来的就不是反相信号了。

2023-12-06 13:57

一般来说,函数里的harmonic list参数就是决定频谱分量的,默认是nil,可以给出所有的频谱分量。取出基波分量可以用于后续的计算,比如计算效率。

2023-12-07 09:33

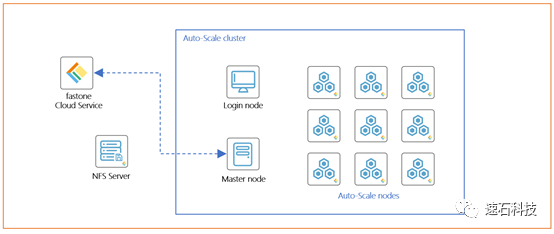

基于 Cadence 30 年的行业知识和领先地位,全新人工智能定制设计解决方案 Virtuoso Studio 采用了多项创新功能和新的基础架构,实现无与伦比的生产力,以及超越经典设计界限的全新集成水平。在本文中,您将了解优异的模拟设计工具如何变得更好,并助您解决挑战性的设计问题。

2024-01-09 12:22

为了满足多模和多频手机对更高性能和更小元件尺寸的需求,业界正在将模块集成策略从单一封装中的类似构建模块转换为采用基于多种技术的多功能前端。这些开发工作针对每个频率范围的、基于单个完全集成的RF模块产品,包括多模/多频功率放大器(PA)、双工器和RF开关等。

2019-03-30 10:43

半导体行业中使用范围最广的EDA应用之一。

2023-08-18 11:14

寄生参数提取(Parasitic Extraction):将版图中的寄生参数提取出来,在Virtuoso中反馈结果,前端工程师会进行后仿验证,重新评估电路特性并进行修改,保证流片正确。

2023-08-16 16:19

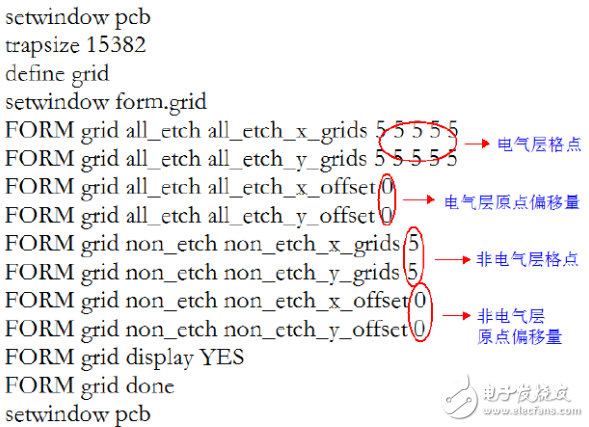

约束驱动的Allegro流程包括高级功能用于设计捕捉、信号完整性和物理实现。由于它还得到Cadence Encounter与Virtuoso平台的支持,Allegro协同设计方法使得高效的设计链协同成为现实。

2018-02-07 14:35