随着FPGA器件尺寸的增大及其内部设计密度的提高,时序收敛面临着前所未有的挑战。由于各种实现工具都竞相满足这种更高复杂性需求,把不同的实现转入量产时间越来越长。为了加快速度,有些设计人员希望能通过云计算来比较分析使用不同实现选项和用户约束决策的效果。

2017-11-18 12:02

为了适应越来越复杂的DSP运算,Virtex-6中嵌入了功能更强大的DSP48E1 SLICE,简化的DSP48E1模块如图5-16所示。

2017-02-11 09:17

Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。

2017-02-11 09:21

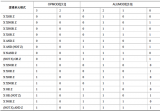

Virtex-6中嵌入BRAM,大大拓展了FPGA的应用范围和应用的灵活性。BRAM可被配置为单端口RAM、双端口RAM、内容地址存储器(CAM)以及FIFO等常用存储结构。

2017-02-11 09:16

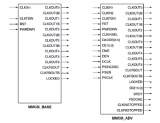

PLL),再到Virtex-6基于PLL的新型混合模式时钟管理器MMCM(Mixed-Mode Clock Manager),实现了最低的抖动和抖动滤波,为高性能的FPGA设计提供更高性能的时钟管理功能。

2017-02-11 09:14

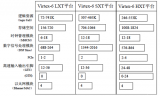

Virtex-6是Xilinx 在2009年2月推出的新一代旗舰产品,采用了第三代Xilinx ASMBL架构、40nm 工艺,提供多达760000 个逻辑单元,为业界成本最低、功耗最低、密度最高、性能最高、带宽最大的FPGA。

2017-02-11 09:04

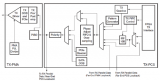

Virtex-6支持多种高速串行接口,其中高速串行模块GTX收发器可以实现150Mbit/s~6.5Gbit/s的线速率。GTX收发器是芯片与芯片之间、板与板之间进行串行通信的首选解决方案。GTX收发器具有以下特性。

2017-02-11 09:26

为了更好的控制时钟,Virtex-6器件分成若干个时钟区域,最小器件有6个区域,最大器件有18个区域。每个时钟区域高40个CLB。在时钟设计中,推荐使用片上专用的时钟资源,不推荐使用本地时钟(如逻辑产生的时钟)。

2017-02-11 09:10

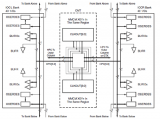

为了能够灵活地验证和实现自主设计的基于NoC的多核处理器,缩短NoC多核处理器的设计周期,提出了设计集成4片Virtex-6—550T FPGA的NoC多核处理器原型芯片设计/验证平台。分析和评估了

2017-11-22 09:15

本设计在基于Xilinx Virtex-6 FPGA内嵌PCI Express Core的基础上,实现了由PCI Express板卡主动发起的DMA读写,可完成PC和PCI Express板卡之间

2017-11-18 10:26