当FPGA开发者需要做RTL和C/C++联合仿真的时候,一些常用的方法包括使用MicroBlaze软核,或者使用QEMU仿真ZYNQ的PS部分。

2023-12-13 10:13

当FPGA开发者需要做RTL和C/C++联合仿真的时候,一些常用的方法包括使用MicroBlaze软核,或者使用QEMU仿真ZYNQ的PS部分。

2023-12-13 10:11

在三天前SpinalHDL1.8.0正式上线,在这次更新中增加了Scala代码和生成的RTL代码之间的对照功能,也就是说我们可以在生成的RTL代码中看到是哪一行Scala生成的,这就为后续的代码调试增加了灵活性(虽然在调试SpinalHDL的时候也很少看对应的

2022-12-09 10:32

对于功耗估算来说,架构阶段为时过早,物理设计阶段为时已晚。有一种趋势是在项目的RTL阶段分析power hot spots。与后期分析相比,基于 RTL 的功耗分析更快、更容易执行,迭代时间更短。

2024-04-05 09:15

数字IC系统逻辑设计这部分主要介绍两个方面,一个是RTL的设计基础;另一方面是verilog基本语法。这一篇文章主要介绍一下RTL的设计基础。

2022-05-17 13:52

百度智能云正式发布了新型 BCC 实例产品 Gr1。不同于其他云服务器,Gr1 所搭载的 Ampere Altra 云原生处理器基于 Arm 指令集架构,采用单线程内核设计,云实例的每一个 vCPU 都是独立的物理核,独享 ALU(逻辑计算单元),缓存等关键物理资

2023-01-11 09:24

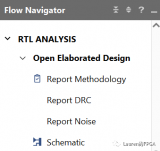

在Vivado FlowNavigator中有一个Elaborated Design,如下图所示,属于RTL Analysis这一步对应的设计。可能很多工程师都没有使用到,而实际上对于代码优化,它是很有帮助的。

2020-10-21 10:56

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

2022-10-11 10:15

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

2022-07-27 09:11

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

2022-11-03 09:14