MII,RMII,GMII接口详细解释 概述: MII (Media Independent Interface(介质无关接口)或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。它

2018-05-18 13:51

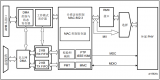

本文主要介绍以太网的MAC(Media Access Control,即媒体访问控制子层协议)和PHY(物理层)之间的MII(Media Independent Interface ,媒体独立接口),以及MII的各种衍生版本——GMII、SGMII、RMII、RGMII等。

2023-04-28 09:43

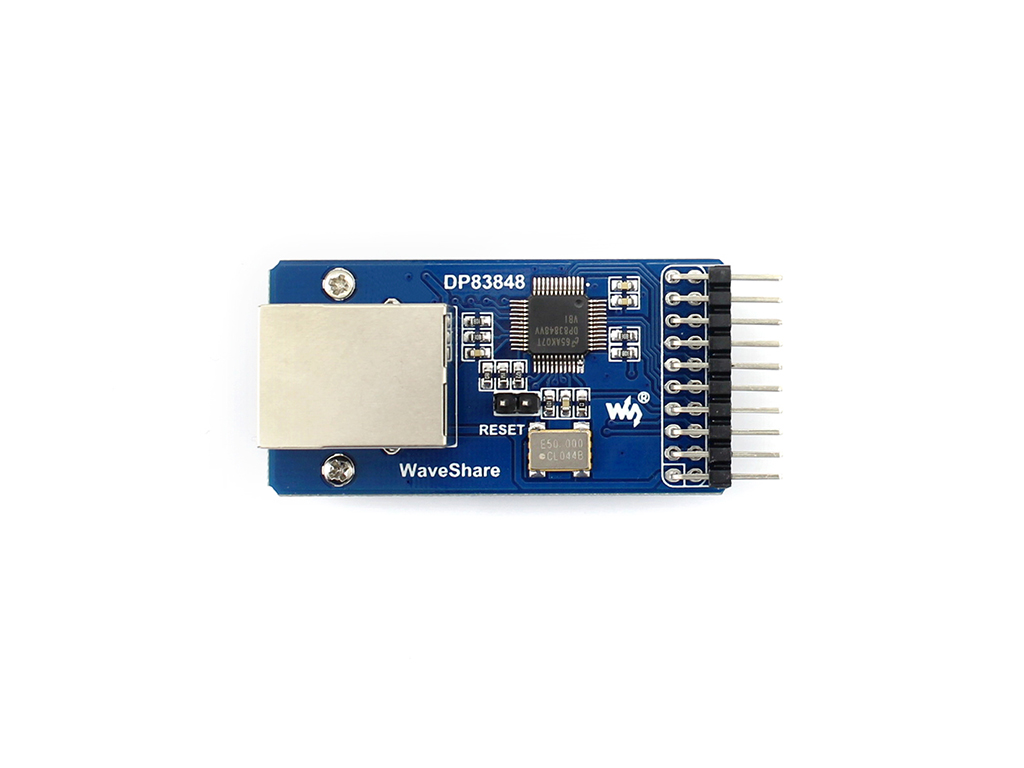

DP83848网络模块 Ethernet 以太网模块 采用RMII接口 高性能10/100Mbps以太网收发器(PHY)低功耗设计 3.3V MAC接口 型号 DP83848 Ethernet Board

2019-12-31 16:27

交换芯片+主控CPU,CPU通过SMI控制交换芯片,CPU提供复位信号和25MHz时钟给交换芯片,交换芯片与CPU数据报文交互通过RMII。主控CPU在boot汇编代码执行交换芯片的复位和25MHz时钟初始化。

2019-01-12 09:09

PHY芯片为OSI的最底层-物理层(Physical Layer),通过MII/GMII/RMII/SGMII/XGMII等多种媒体独立接口(介质无关接口)与数据链路层的MAC芯片相连,并通过MDIO接口实现对PHY状态的监控、配置和管理。

2023-05-04 10:06

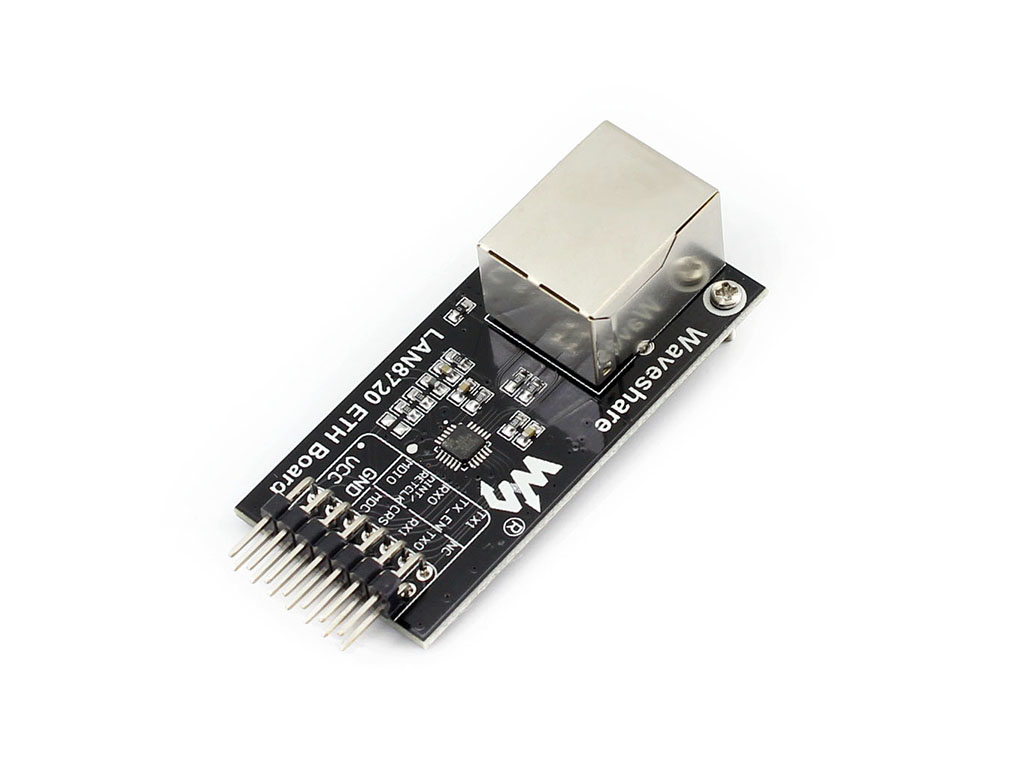

LAN8720以太网模块 以太网收发器(PHY)采用RMII接口 高性能10/100Mbp, 超低功耗设计, 可使用3.3V单电源供电, 支持HP Auto-MIDX 型号 LAN8720 ETH Board

2019-12-30 15:07

PHY芯片为OSI的最底层-物理层(Physical Layer),通过MII/GMII/RMII/SGMII/XGMII等多种媒体独立接口(介质无关接口)与数据链路层的MAC芯片相连,并通过MDIO接口实现对PHY状态的监控、配置和管理。

2023-07-26 11:46

CKS32F4xx系列芯片自带以太网模块,该模块包括带专用DMA控制器的MAC 802.3(介质访问控制)控制器,支持介质独立接口(MII)和简化介质独立接口(RMII),并自带了一个用于外部PHY通信的SMI接口,通过一组配置寄存器,用户可以为MAC控制器和DMA控制器选择所需模式和功能。

2023-11-10 11:15