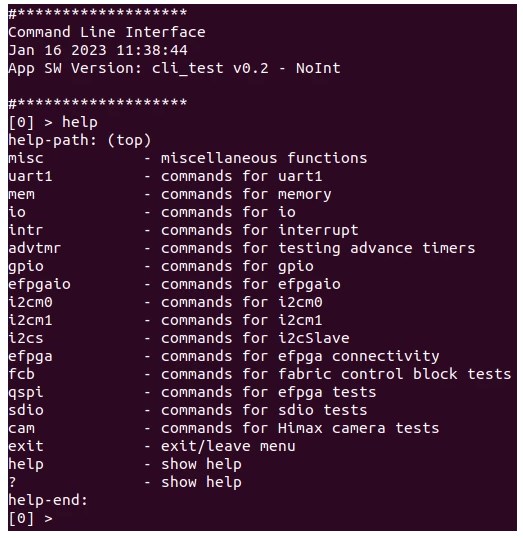

OPENHW提供了基于FreeRTOS的示例工程,由于使用的是PLCT提供的QEMU,所以IDE中自带的工程并不能直接使用,为了避免不必要的麻烦,本文采用PLCT提供的示例工程。

2023-02-01 10:05

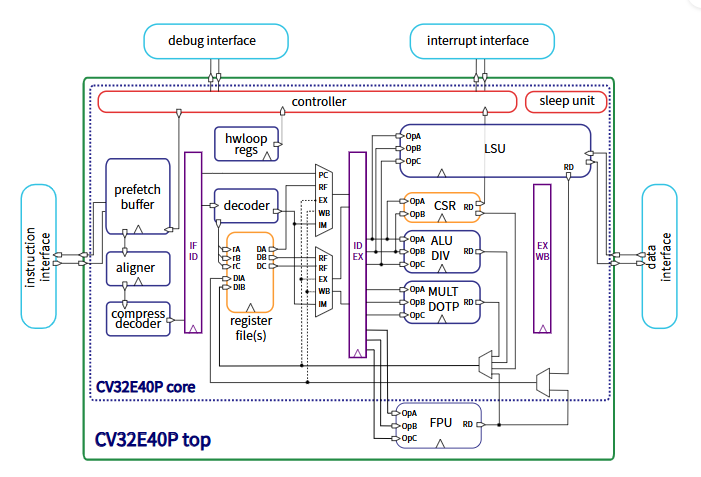

CV32E40P 是 OpenHW Group 推出的开源 RISC-V 处理器 IP 内核,基于 PULP 平台的 RI5CY 内核演进而来,专为高效嵌入式系统设计。以下从技术架构、性能特性

2025-04-10 15:44

本次实验验证的平台是PLCT提供的QEMU,在Linux下的QEMU可以使用上述的笔者编译好的,也可以使用自己尝试编译PLCT提供的源码。

2023-10-13 14:58

由中国电子学会主办,美国赛灵思公司和北京工业大学共同承办的“FPGA助力中国智造,拥抱嵌入式计算新时代 — 第三届OpenHW开源硬件与嵌入式大赛”总决赛于今天在北京工业大学隆重举行。来自中国大陆

2018-06-05 13:45

2016开源硬件与全可编程技术论坛暨Xilinx中国大学合作十周年庆典于今天在上海召开。本活动由Xilinx公司与上海交通大学共同主办,将有200多位专家学者分享技术趋势和业界动态,研讨科研和教学经验。活动将成为国内全可编程技术的一次盛会。 从2006年设立中国大学合作部门开始,Xilinx大学合作在中国已走过10个春秋,得到了中国高校老师的广泛认可。在过去10年中,Xilinx从一家具有可编程逻辑优势的公司转变为拥有“All Programmable”(全可编程)优势的

2017-02-08 07:28

UltraSoC将通过与OpenHW集团(OpenHW Group)合作以提供其业界领先的RISC-V追踪编码器的开源项目。

2019-12-11 17:54

的具体设计。当前,有几种实现方法,商业化的设计,如Si-Five和Andes;完全开源的,如OpenHW组织(OpenHW Group)和LowRISC。Silicon Labs是OpenHW组织

2020-06-08 16:48

今天,赛灵思OPENHW2017教师峰会暨创新大赛决赛在新加坡科学技术大学举行。赛灵思亚太区高级副总裁兼亚太区总裁汤立人在会上分享了四大技术趋势。

2018-06-29 10:56

北京,由中国电子学会主办,美国赛灵思公司和北京工业大学共同承办的“FPGA助力中国智造,拥抱嵌入式计算新时代 — 第三届OpenHW开源硬件与嵌入式大赛”总决赛于今天在北京工业大

2012-06-04 17:12

(2) CORE-V(OpenHW Group) 特点 :开源RISC-V处理器家族,支持AI加速扩展(如DSP/向量指令)。 代表IP :CV32E40P(支持自定义AI协处理器)。 适用场景 :低功

2025-04-02 17:44