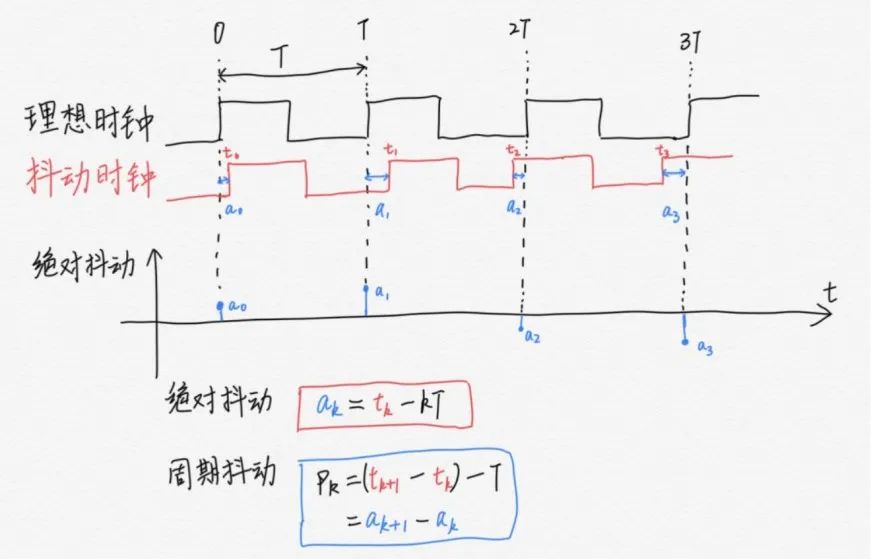

在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。但不幸的是,这种信号并不存在。如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。这种不确定就是抖动(jitter)。

2018-03-13 10:21

时钟电路是芯片中最基础的电路,时钟电路性能的好坏关乎SoC中所有电路能否达到预期目标,例如:计算核(CPU/GPU/NPU)的主频,DDR的带宽,高速接口(PCIE)的带宽等。

2022-10-12 15:08

Discrete Jitter是由MMCM/PLL引入的,其具体数值可通过点击图2中Clock Uncertainty的数值查看,如图5所示。通常,VCO的频率越高,引入

2018-11-12 14:40

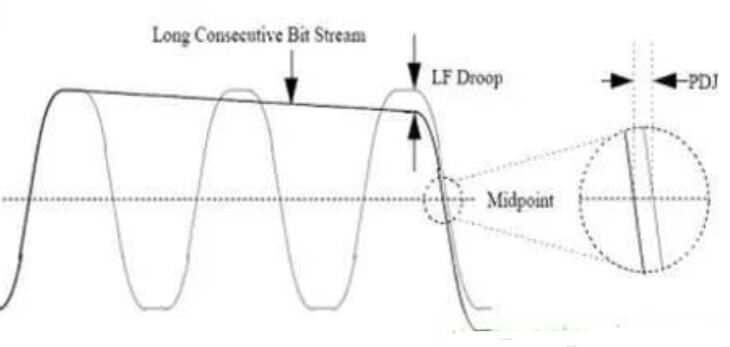

我们知道串联信号中的一系列交流耦合电容可以提供直流偏置和过流保护,但这也会给链路PDJ(Pattern-Dependent Jitter,图形相关抖动)带来另一个问题。

2021-04-03 16:00

【序文】近年,伴随影像传输等普及,骨干网中流过的通信量有增无减,通信的高速、大容量化进展迅速。在这种情况下,高速化通信基础设施对高频且输出信号稳定的基准信号源的需求十分强烈。抖动(Jitter

2024-08-14 16:52 Piezoman压电侠 企业号

数字示波器的抖动噪声基底(Jitter Noise Floor)指标经常会被误会和误用,那么抖动噪声基底到底是什么?抖动噪声基底是示波器本身对抖动测量结果贡献的整体噪声,它经常被标定为统计结果,用有效值或标准偏差值(在平均值为0时,标准偏差值和有效值相同)来表示。

2019-08-30 16:04

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20

抖动(Jitter)反映的是数字信号偏离其理想位置的时间偏差。高频数字信号的bit周期都非常短,一般在几百ps甚至几十ps,很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。

2015-10-02 17:21

这里将介绍SERDES的基本概念,并介绍SERDES相关的专有名词:眼图(Eye-diagram)、眼图模板、抖动(Jitter)、容忍度(tolerance)、功耗(Power Consumption)、预加重(Pre-emphasis)、均衡(Equalization)、8B/10B编码等。

2018-01-30 08:55

绝对抖动 (Absolute Jitter) 是一个衡量时间点的不确定性概念,参考为理想时钟的时间点,该相对偏差量可能表示为一个离散时间的随机变量。绝对抖动造成的时间点不确定性可能会对很多采样电路

2024-08-22 16:19