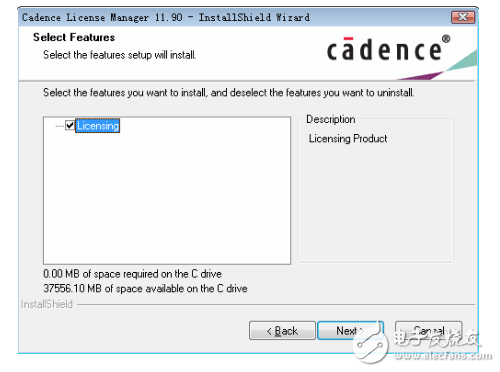

在Allegro中如何进行skill的安装,下面就以下载FanySkill工具为例。

2022-10-17 11:03

在电路设计中,原理图中常以一个功能模块的器件绘制在同一页面上,因此,通常将器件在pcb按页摆放在一起,更方便进行模块化布局。为此,Fany skill添加了将pcb中的器件按照原理图页,进行分类摆放的功能。需要注意的是,此功能需要在将器件导入PCB之后,才可执行此操作。

2025-04-23 17:10

5G时代已来,作为老旧制式,3G网络正在退出历史舞台!日前,德国沃达丰宣布于2021年6月30日前彻底关闭3G(UMTS)网络,以腾退3G频率资源,重耕给更高效率的4

2020-09-01 15:02

中国四大运营商在2G-5G频段划分范围详细数据

2020-09-01 15:08

DFM(Design for Manufacturability,可制造性设计);是指产品设计需要满足产品制造的工艺要求,具有良好的可制造性,使得产品以最低的成本、最短的时间、最高的质量制造出来。

2025-07-17 10:32

由于skill 语言提供编程接口甚至与C 语言的接口,所以可以以Cadence 为平台进行扩展用户,还可以开发自己的基于Cadence 的工具。实际上整个Cadence 软件可以理解为一个搭建在skill语言平台上的可执行文件集。所有的Cadence 工具都是用

2018-02-07 10:42

在软件使用过程中通常需要英制单位和公制单位进行切换;PCB制造商通常对设计文件有特定的单位要求;在团队协作中,不同成员可能习惯使用不同的单位制(英制或者公制),单位换算可以确保设计文件的准确性、兼容性和可制造性。通过合理的单位换算,可以避免设计误差、满足制造要求,并提高团队协作效率。因此,单位换算是PCB设计过程中不可或缺的一部分。

2025-08-06 11:48

在进行高速PCB设计的过程中,我们经常会遇到一个问题,那就是当PCB板的叠层结构发生变化时,为了保持信号的完整性,我们不得不对高速信号线的线宽进行相应的调整。那么这种调整是必要的,因为不同的叠层结构会对信号的阻抗产生影响。手动去逐一更改这些高速信号线的线宽是一项非常繁琐且耗时的工作,它不仅不能提高我们的设计效率,反而会因为工作量巨大而降低整体的设计效率。

2025-06-04 17:21

在Allegro PCB设计系统中,格点设置需点击菜单栏"Setup > Design Parameters..."选项,在“Design Parameter Editor”对话框中点击"Setup grids"选项,如图1所示,然后在弹出的"Define Grid"窗口中配置参数,如5等份1mil的间距,如图2所示。该流程涉及多层窗口跳转,操作较为繁琐,相比之下,FanySkill提供的"格点"功能实现了更高效的设置方式,只需一键即可快速完成格点的调整,省去了复杂的菜单导航过程。

2025-05-19 15:04

过使用“远程抓取器件”功能,用户可以批量选取多个器件,随后通过鼠标左键逐个点击放置,实现高效精准的器件布局。该功能特别适用于在大规模芯片周边配置去耦电容、电阻等元件,能够快速将元件定位到目标焊盘附近或芯片背面。

2025-05-08 10:34