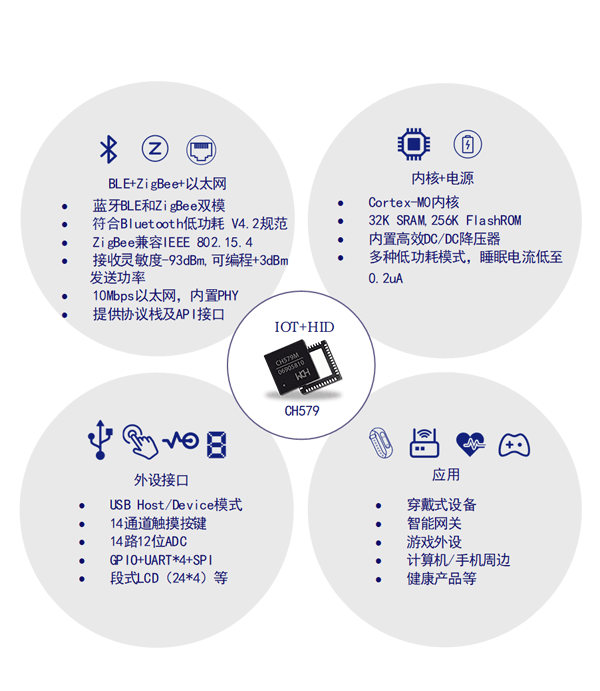

本方案基于一套硬件结构,通过软件的升级方便地实现HID类和CDC类产品之间的转换。

2012-05-24 10:06

每一个外部中断都有一个对应的优先级寄存器,Cortex-M0中NVIC-IPR共有8个寄存器,而每个寄存器管理4个IRQ中断,所以M0的IRQ中断源最多只支持32个,再加上16个内核中断,也就是说M0最多48个中断源

2023-03-20 09:28

Cortex-M0处理器允许两种形式的中断请求:电平触发和脉冲输入。

2022-05-13 12:05

在Cortex‐M0内核上搭载了一个异常响应系统,支持众多的系统异常和外部中断。其中,编号为1-15的对应系统异常,大于等于16的则全是外部中断,优先级的数值越小,则优先级越高。除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。

2022-06-01 14:41

IAP ( In Application Programming )功能为产品软件升级提供了一个方便快捷的接口。用户可以通过串口、USB、CAN总线[1]而无需使用编程器即可实现产品的软件更新,甚至可以通过以太网[2]或者无线网络[3]实现产品软件的远程升级,大大方便了产品的功能迭代,提升了产品的易用性。

2023-12-05 11:05

我们使用的处理器都有一套架构,比如intel 酷睿 i5 属于X86架构,再比如STM32F0是Cortex-M0内核,属于ARMv6-M架构。

2022-03-21 10:19

意法半导体(ST)5月15日在北京媒体沟通会上宣布,开始量产基于ARM Cortex-M0处理器内核的入门级STM32 F0系列32位MCU。其适于工业控制器、家庭自动化、打印机和白色家电等应用。

2012-05-23 11:00

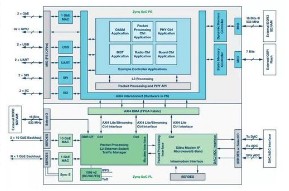

首先是内核的选择。LPC4350基于32位的ARM Cortex-M4和Cortex-M0内核(以下简称M4和M0),两个内核均可在高达204MHz的主频下执行代码。

2018-09-21 09:39

特 点 > 32位ARM Cortex-M0内核,最高40MHz系统主频 > 内置32K SRAM,250KB CodeFlash,2KB DataFlash, 4KB

2019-10-18 10:40

本文介绍了EM773主要特性和优势,方框图,智能电表原理方框图,电表主要元件BOM以及智能电表无线插头电表电路图和电表指标。 NXP 公司的EM773是基于ARM Cortex-M0的低功耗32位

2010-10-15 15:36