Design Compiler 2010将综合和布局及布线的生产效率提高2倍 实现了与布局和布线检测5%的关联度,以及在多核技术上的2倍速更快的运行时

2010-04-07 08:59

emory是大家Floorplan中经常使用到一个器件,而且需要花费不少时间去摆放它。

2018-07-05 11:02

Custom Compiler™将定制设计任务时间由数天缩短至数小时,消弭了FinFET的生产力差距。

2016-04-13 15:23

简介 3DIC Compiler具有强大的Bump Planning功能。它可在系统设计初期阶段没有bump library cells的情况下,通过定义pseudo bump region

2022-11-24 16:58

先进封装从MCM发展到2.5D/3D堆叠封装,目前发展最快的制造商是TSMC。TSMC从Foundry端延伸入2.5D/3D先进封装,称为3D Fabric。近十年来TSMC的2.5D先进封装技术经历了5代更新,硅载板的面积已经达到3倍光罩尺寸,最新技术可以集成8个HBM,支持eDTC,同时改进了TSV和TIM材料,以及厚铜互连,对于3D堆叠的PI、SI、Thermal和Stress等方面都有了很好的的改善。与此同时NVIDIA的A100单芯片面积为826mm2,逼近光罩尺寸极限,而大芯片面临低良率、成本增加的问题,这直接导致了Chiplet技术成为炙手可热的话题。TSMC在SoIC的未来十年的计划中描述每两个相邻工艺节点的bump pitch缩小70% ,从而达到每工艺节点2倍带宽密度的扩展,以及EEP(Energy Efficiency Performance)提升。

2022-10-26 10:21

原文标题:Design Compiler再进化:助力开发者更快实现终极KPI 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-06-26 18:40

最新版IC Compiler II通过新一代分布式并行、智能场景管理、高效基础设施扩展和固有核心引擎算法,提供快2倍的吞吐量

2019-08-13 16:23

原文标题:本周五|Design Compiler再进化:助力开发者更快实现终极KPI 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-06-27 17:35

原文标题:明天开课|Design Compiler再进化:助力开发者更快实现终极KPI 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-06-29 19:15

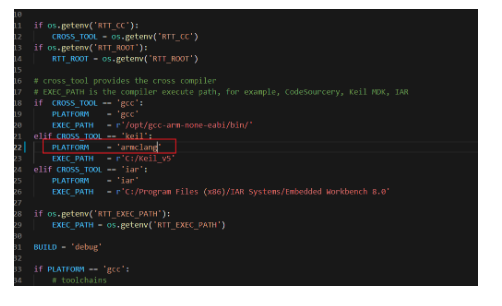

在 RT-Thread 4.1.0 正式发布版中,添加了对 Arm Compiler 6 的支持,用户可以修改 rtconfig.py 指定生成 mdk5 工程时使用的编译器

2022-06-01 15:20