的用武之地。在最新的Ultrascale系列FPGA中,IODelay这一单元的具体用法,跟7Series中相比产生了一些变化。本文总结下,供读者参考

2017-11-16 01:26

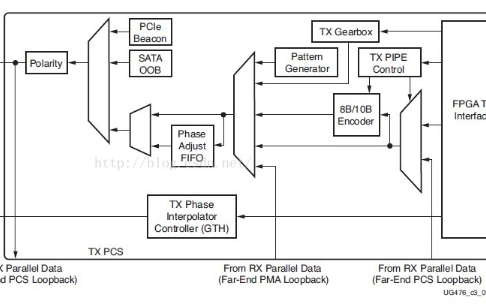

FPGA内部并行数据通过FPGATX Interface进入TX发送端,然后经过PCS和PMA子层的各个功能电路处理之后,最终从TX驱动器中以高速串行数据输出。

2020-03-29 17:09

Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品。如图2.1所示,在相对较高层次对比了三种器件。Zynq MPSoC的PS部分比Zynq的PS部分面积更大,也更复杂。本章,将介绍这三种器件的特点.

2022-08-15 09:16

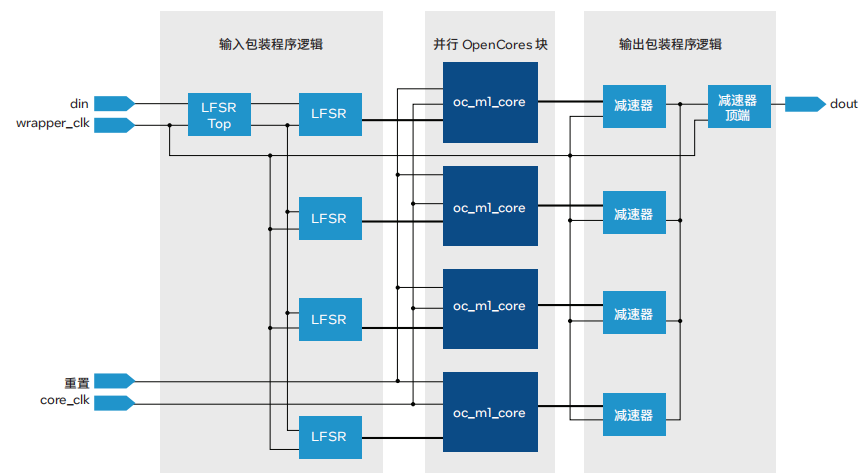

与同类FPGA相比,Agilex 7 FPGA可为OpenCores公开发布的设计提供超过一个速度等级的内核性能提升。

2024-08-30 17:07

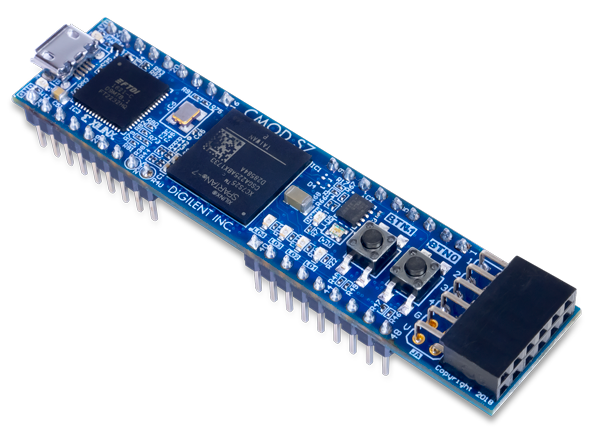

Digilent Cmod S7是一款小巧的48引脚DIP板,采用36引脚,围绕Xilinx Spartan-7 FPGA构建。它有32个FPGA数字I / O信号,2

2019-11-14 15:55

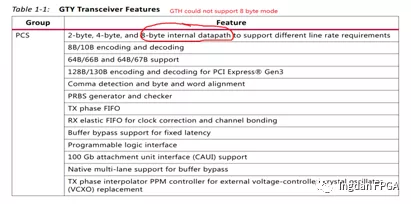

的速率和带宽效率。 今天我们来聊一聊7 Series、Ultrascale系列GTH与Ultrascale+ GTY的内部区别。

2022-08-02 11:28

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给

2021-05-01 09:47

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Ge

2024-11-05 15:45

GTX RX接收端的结构和TX发送端类似,数据流方向相反,不过和发送端也有一些区别,GTX的RX接收端结构图如图1所示: 图1 下面将根据数据流方向介绍一下RX接收端各个电路部分的功能。 RX Equalizer (DFE and LPM):RX信号从AFE(模拟前端)进来之后,首先经过RX均衡器,均衡器的主要作用是用于补偿信号在信道传输过程中的高频损失,因为信道是带宽受限的,所以信号经过它必将造成衰减甚至遭到破坏。

2017-11-10 14:49

今天咱们聊聊xilinx7系列FPGA配置的相关内容。总所周知FPGA上电后,其工作的逻辑代码需要从外部写入FPGA,FPGA

2019-10-20 09:02