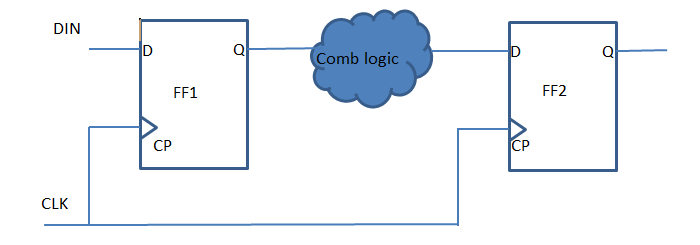

建立时间和保持时间是SOC设计中的两个重要概念。它们都与时序分析有关,是确保芯片正常工作的关键因素。

2023-08-23 09:44

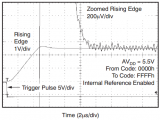

本篇仿真介绍放大器的建立时间,也称为上升时间。它是高速放大电路、或在SARADC驱动电路设计时,需要谨慎评估的参数。

2021-02-15 16:37

今天,我们将介绍两种相关的动态参数 — 压摆率与建立时间。如欲了解更多有关静态和动态参数的不同之处,敬请参阅本文。

2018-07-10 16:14

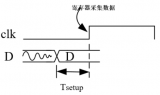

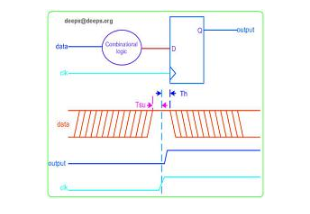

我理解这个D触发正常运转要满足四个约束,第一个是建立时间,第二个是保持时间,第三个是对于最后一个传输门的关断时间的控制,第四个是[时钟周期]() 约束。

2023-12-04 15:44

文件提到两种setup/hold测量方式:10% push-up和pass/fail,按照TSMC说法,前者会更乐观一些,因此如果是采用前者(10% push-up)的测量方式得到建立时间和保持时间,需要十份小心时序裕量是否足够,最好人为添加margin。

2023-12-05 11:19

本文将介绍一种新方法,其经过证明可以有效地完成这些测量工作。它是一种相对低成本、简单的建立时间测量方法。这种方法把准确性和精确度建立在波形生成器和采样保持电路的相

2012-07-27 10:25

建立时间;保持时间;建立时间裕量;保持时间裕量

2018-12-01 08:20

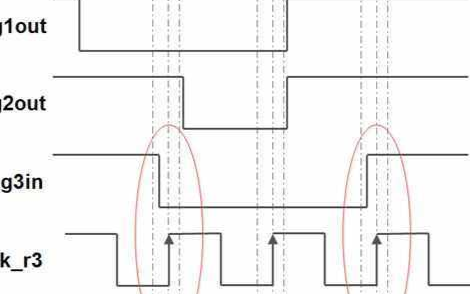

不论数字信号的上升沿是抖还是慢,在信号跳变时,总会有一段过渡时间处于逻辑判断阈值的上限和下限之间,从而造成逻辑的不确定状态,更糟糕的是,通常的数字信号都不止一路,可能是多路信号一起传输来代表一些逻辑

2023-11-29 16:36

时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-06-19 15:04

时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错。

2020-06-26 10:37