本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB

2014-07-24 11:11

在开发过程中硬件调试不免会遇到一种情况,就是可能SD卡、USB和网口都没有调通,但是需要一些少量数据对特定功能进行验证,这时通过JTAG接口Restore数据到DDR或从DDR Dump数据到PC机不失为一种有效选择。

2017-02-08 16:21

Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品。如图2.1所示,在

2022-08-15 09:16

该参考设计采用多种 TPS54325 和其他 TI 电源器件,是适用于 Xilinx Zynq FPGA 的全套电源解决方案。输入电压达到 12V 后,该参考解决方案可提供 Zynq FPGA 所需的所有电源轨(包括 DDR

2017-02-11 09:39

目前我在我的zynq 开发版上测试,成功将根文件系统扩容到336M,至于为什么只能扩容到336M,暂时还没找到相关的资料(我的zynq 开发版硬件ddr3是4G,内存是512M),如果有知道原因的,恳请留言评论,在此

2022-10-17 09:19

本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数

2018-02-06 18:47

在ps的控制下,可以实现安全或非安全的配置所有ps和pl。通过zynq提供的JTAG接口,用户可以在外部主机的控制下对zynq进行配置,zynq不支持最开始就配置pl的过程。

2019-05-15 11:41

普通的 FPGA 一般是可以从 flash 启动,或者被动加载,但是ZYNQ不行,ZYNQ必须PS端参与

2022-07-22 10:10

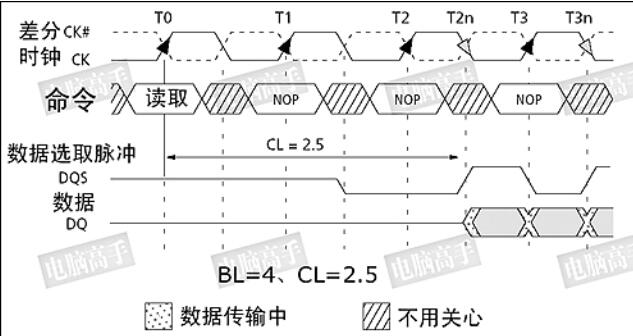

DDR是Double Data Rate的缩写,即“双倍速率同步动态随机存储器”。DDR是一种技术,中国大陆工程师习惯用DDR称呼用了DDR技术的SDRAM,而在中国台

2023-07-16 15:27

DDR=Double Data Rate双倍速率同步动态随机存储器。严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,其中,SDRAM 是Synchronou

2018-05-23 16:07