因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V

2020-01-01 17:27

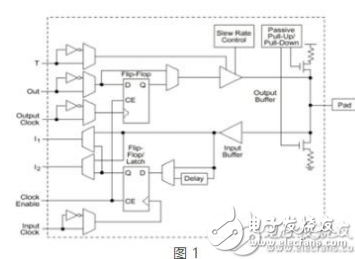

在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚分配产生非常重要的影响。这篇专题就针对FPGA从上电开始 ,配置程序,到正

2017-11-28 14:41

该项目演示如何在 Zynq SoC 上开始使用 FreeRTOS。

2023-10-18 09:44

Step3: 按照“Vivado中进行ZYNQ硬件部分设计”中介绍的,直到在SDK中编写C代码步骤。需要使用UART进行通行,分为通过UART向外发送数据和通过UART接收数据。

2023-09-23 09:25

这篇博文特别关注 Zynq SoC 的多用途 IO (MIO, Multipurpose IO) 模块。

2022-03-30 11:43

本教程介绍了如何使用μC/ OS BSP建立在ZYNQ基本应用程序®使用Vivado -7000 ™ IDE和赛灵思® SDK。在本教程中,您将使用Vivado IP集成器配置ZYNQ处理器系统以及

2017-11-17 15:06

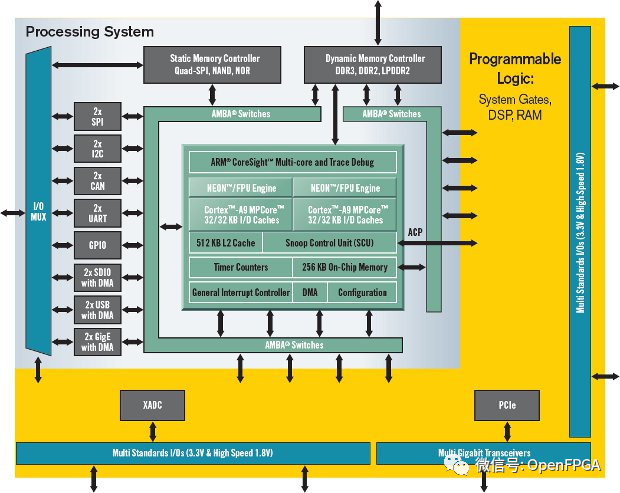

Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品。如图2.1所示,在

2022-08-15 09:16

它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。

2018-09-03 16:27

芯片设计工程师常常需要根据输入输出信号(Input and Output, I/O)实现管脚电平数字逻辑。例如,系统工程师利用微控制器进行时钟增殖时常常需要创建时钟树,将输入时钟输入至多个缓冲时钟(具有适当的驱动能力),和/或倒转时钟极性。还有许多场景下,系统工程

2018-04-07 10:04

本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式评估板上实现多个 UIO,同时借助赛灵思的工具完成硬件工程和 linux BSP 的开发,最后通过测试应用程序完成测试。

2018-03-21 14:55