本视频介绍了设置和测试Xilinx PCIe DMA子系统性能的过程。

2018-11-27 06:16

最近弄PCIE,遇到一个问题,以前我们总认为:Xilinx的PCIE core的管脚是固定的,即指定了PCIE core的位置,对应的管脚也就指定了,真实情况是怎么样的

2023-11-17 17:02

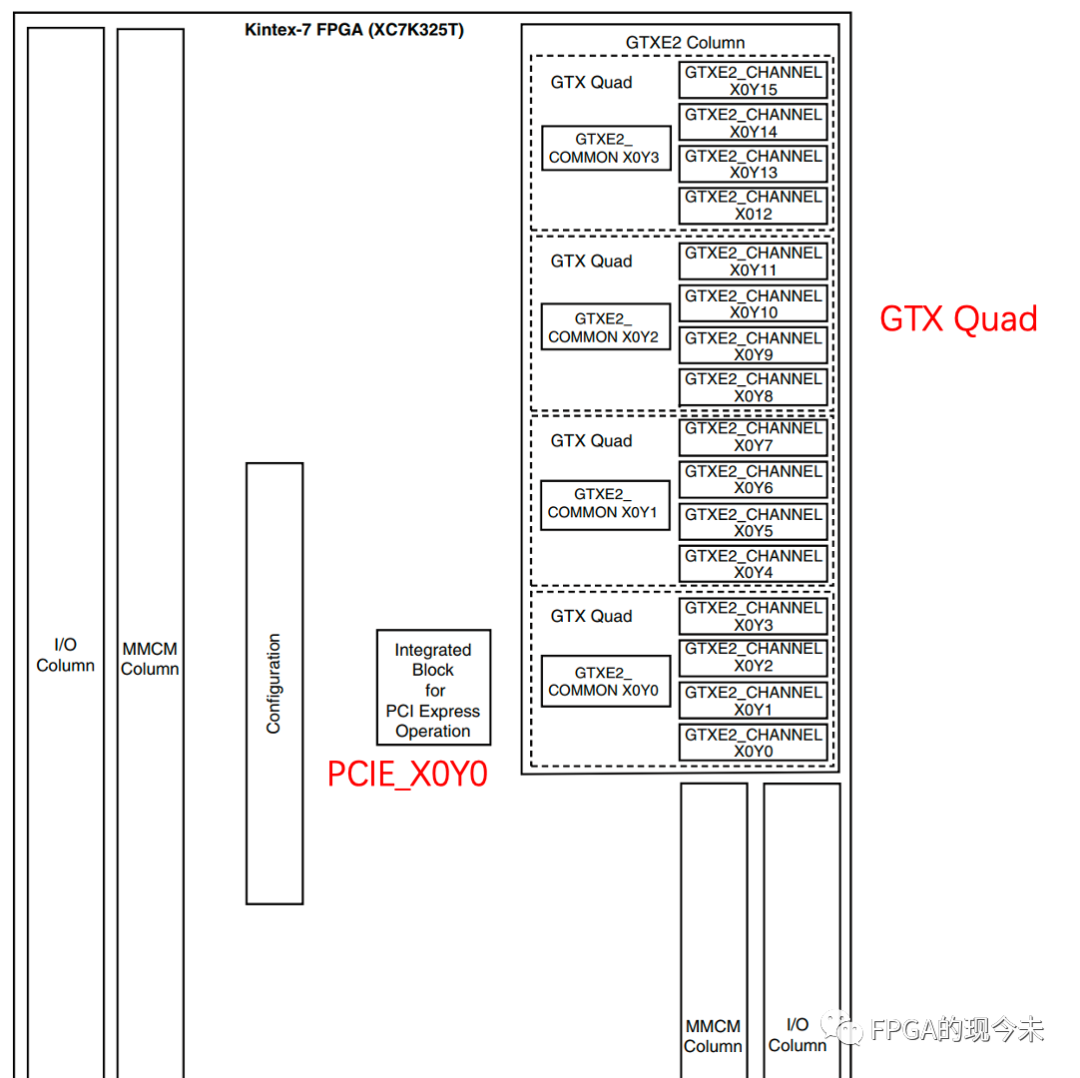

一个GT Quad由四个GT车道组成。为PCIe IP选择GT Quads时,Xilinx建议您在最靠近PCIe硬块的地方使用GT Quad。虽然这不是必要时,它将改善设计的位置,路线和时间。

2023-03-30 09:41

根据PCIe的协议,当设备启动后,PCIe设备必须满足启动时间的要求,即上电后100ms内,完成PCIe设备的初始化。如果不能满足PCIe设备启动时间的要求,则lspc

2017-02-07 20:55

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及一些特性。

2024-11-05 15:45

在EDK环境中针对在xilinx sp605 PCIe开发板,举一个简单的例子,介绍如何使用PCIE核与PC进行数据通讯。

2018-06-07 02:46

: 总结上文:在硬件设计引脚分配的时候我们需要知道: 1、一个GT Quad由四个GT车道组成。为PCIe IP选择GT Quads时,Xilinx建议您在最靠近PCIe硬

2021-06-27 11:20

的可靠性传输,热插拔以及服务质量(QOS)等功能 下面是关于 PCIE PCB 设计的规范: 1、从金手指边缘到 PCIE 芯片管脚的走线长度应限制在 4 英寸

2022-11-30 17:27

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡,支持2x72bit(数据位宽64bit+ECC)DDR4存储,数据传输速率 2400Mb/s。DDR4单簇容量4GB,两组总容量为8GB

2024-11-14 11:30

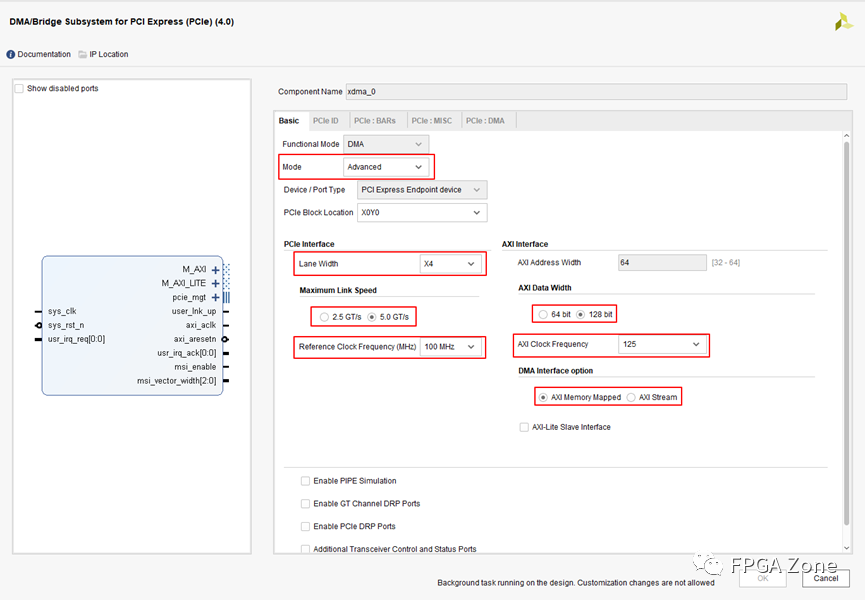

本文介绍一个FPGA开源项目:PCIE通信。该工程围绕Vivado软件中提供的PCIE通信IP核XDMA IP建立。Xilinx提供了XDMA的开源驱动程序,可在Windows系统或者Linux系统下使用,因此采用X

2023-09-04 16:45