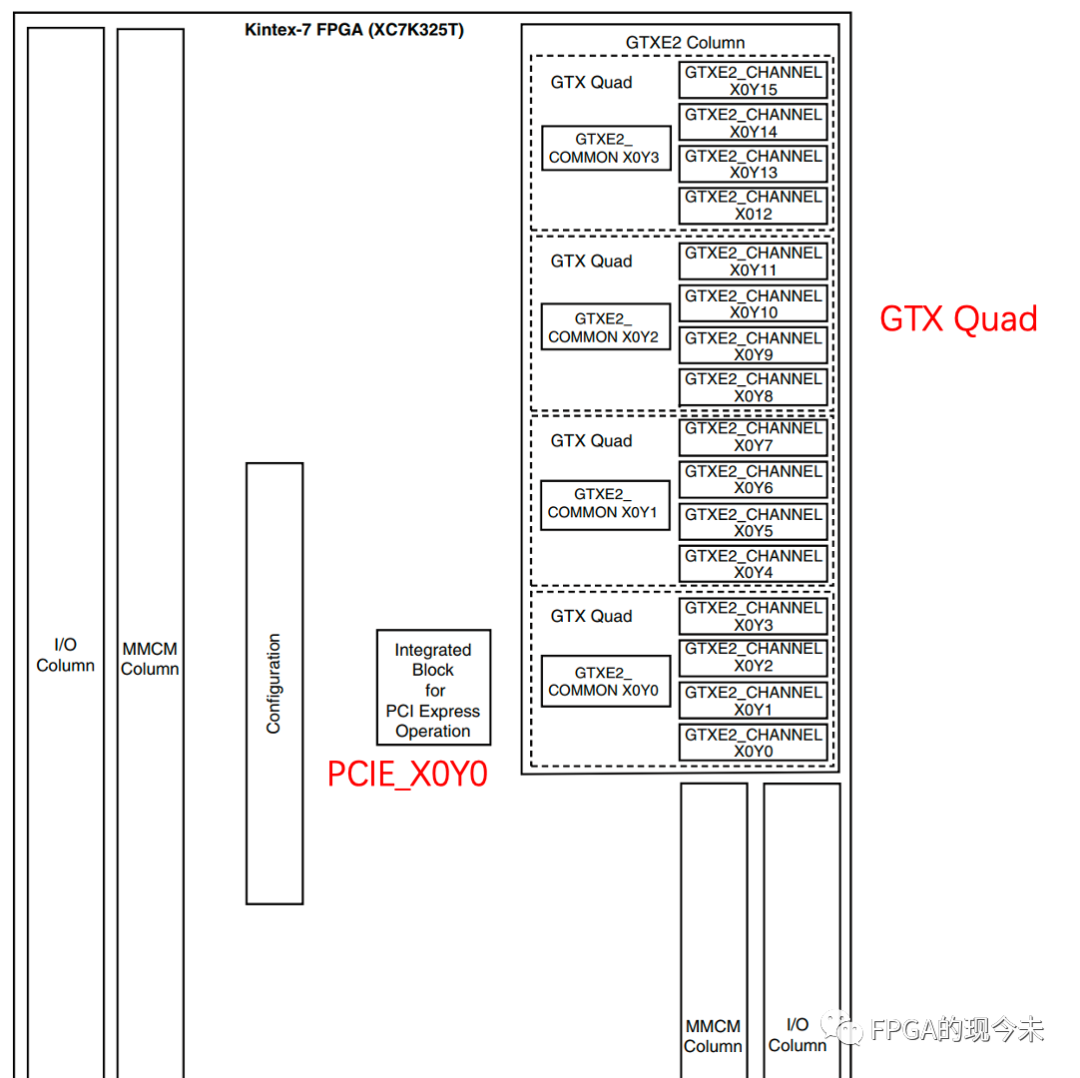

最近弄PCIE,遇到一个问题,以前我们总认为:Xilinx的PCIE core的管脚是固定的,即指定了PCIE core的位置,对应的管脚也就指定了,真实情况是怎么样的

2023-11-17 17:02

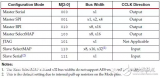

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及一些特性。

2024-11-05 15:45

PCIe 仿真需要Endpoint 模型和Root Port 模型协同工作。用户一般可以采用购买BFM/VIP 来模拟对端模型也可以自己设计对端模型,更简便的方法则是使用Xilinx 提供的模型 (Xilinx Ro

2022-06-08 15:30

上一篇内容我们已经对PCIE协议进行了粗略的讲解。那么不明白具体的PCIE协议,我们就不能在FPGA中使用PCIE来进行高速数据传输了吗?答案是否定的。因为Xilinx

2022-06-01 15:52

随着英特尔Alder Lake CPU的发布,以及AMD 7000 Ryzen CPU的即将发布,PCIe 5.0 硬件终于成为现实。但什么是 PCIe 5.0?

2023-11-18 16:48

目前通过 FPGA 实现 PCIe 接口是一种比较常用的方式,具有硬件成本低、可靠性高、灵活性大、易于升级等优势。两大 FPGA 厂商 Xilinx 和 Altera均具有完善的接口 IP 和测试方法。

2019-03-24 09:21

该信号为全局复位信号,由处理器系统提供(RC),处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设

2018-12-22 14:45

如图所示,PCIe IP作为endpoint与RC对接,用户实现了应用逻辑,与PCIe IP进行交互,交互信号中data格式为TLP报文格式,且交互信号包含相应的控制信号,例如PCIe配置空间和IP相干的配置信号。

2024-02-26 18:19

首先说一下xapp1052模块的组成结构:顶层模块是xilinx_pci_exp_ep,在顶层模块中包含pci_exp_64b_app和bmd_design两个模块,其中pci_exp_64b_app就是我们要介绍的重点,而bmd_design则是实现PCIE协议

2018-07-11 08:47

根据PCIe的协议,当设备启动后,PCIe设备必须满足启动时间的要求,即上电后100ms内,完成PCIe设备的初始化。如果不能满足PCIe设备启动时间的要求,则lspc

2018-06-19 10:24