BRAM和URAM都可级联,只是级联方式不同。在使用BRAM时,我们只需要设定宽度和深度,并根据时钟频率合理选择Latency,也就是选择是否需要使用BRAM自带的输出

2019-03-06 15:44

UltraRAM 原语(也称为 URAM)可在 Xilinx UltraScale +™ 架构中使用,而且可用来高效地实现大容量深存储器。

2019-07-13 11:08

UltraRAM 原语(也称为 URAM)可在 Xilinx UltraScale + 架构中使用,而且可用来高效地实现大容量深存储器。由于大小和性能方面的要求,通常这类存储器不适合使用其他存储器

2023-05-08 15:15

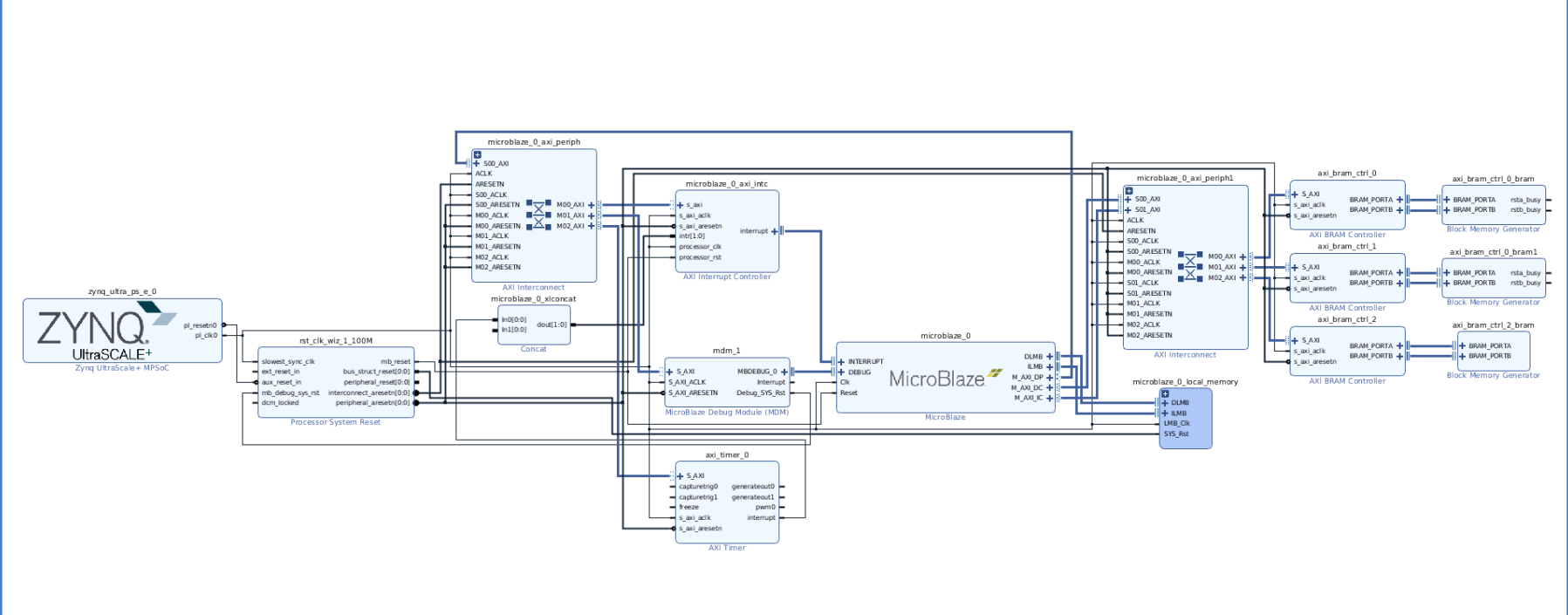

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultr

2022-08-02 10:09

本篇博文旨在演示如何通过 NoC 从 Versal 应用处理单元 (APU) 访问 AXI BRAM。

2022-11-09 10:24

当整体资源利用率达到70%~80%时(对于多die芯片,这个数值是指每个SLR的资源利用率),需要砍掉一些模块以降低资源利用率。尤其要避免LUT/BRAM/DSP/URAM利用率同时出现大于80%的情形。如果BRAM

2018-10-30 10:47

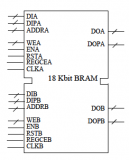

Spartan-6中的BRAM存储18Kbit数据,能配置成两个独立的9Kbit BRAM或者一个18Kbit BRAM。每个RAM可以通过两个端口寻址,也可以配置成单口RAM。

2017-02-11 08:49

我们需要关注两类路径。一类路径是由纯粹的CLB中的资源(FF,LUT,Carry,MUXF)构成的路径;另一类则是Block(DSP,BRAM,URAM,GT)之间的路径。

2018-10-27 08:43

Virtex-6中嵌入BRAM,大大拓展了FPGA的应用范围和应用的灵活性。BRAM可被配置为单端口RAM、双端口RAM、内容地址存储器(CAM)以及FIFO等常用存储结构。

2017-02-11 09:16

最近在做一个GUI的项目,想试着用FPGA实现一个简单的GUI。硬件基本模块和整个硬件系统已经完成设计,但是软件程序上还处在调试阶段,由于程序比较大,FPGA内部的BRAM已经完全不够用了,只能将运行的程序放到DDR DRAM中

2017-02-11 11:41