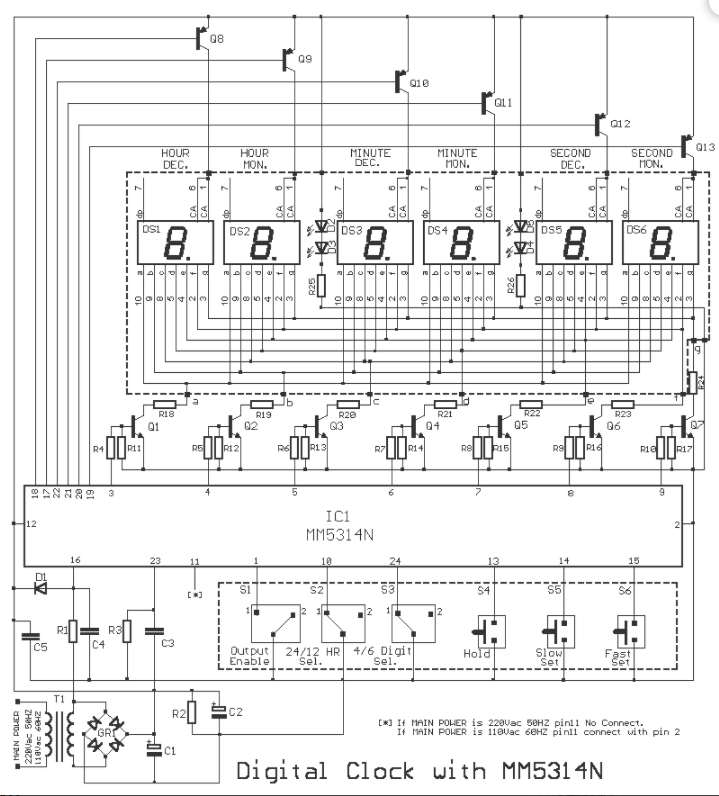

这是基于IC MM5314N的数字时钟电路图。时钟显示使用 6 个 7 段 LED,格式为 HH:MM:SS。该电路的电源已包含在内,因此您可以将该电路直接连接到电源。

2022-06-21 16:41

FPGA本身是有专门的时钟cell的,以xilinx FPGA为例,就是primitive库中的BUFG。

2018-12-22 15:33

每一个收发器拥有一个独立的发送端,发送端有PMA(Physical Media Attachment,物理媒介适配层)和PCS(Physical Coding Sublayer,物理编码子层)组成

2018-06-20 13:48

在本文中,我们来学习下如何找到连接到服务器的客户端计算机的IP地址。我们将创建一个简单的客户端-服务器场景,让我们探索用于TCP/IP通信的 java.net API。 背景 Java应用程序

2023-10-08 11:37

xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟

2022-07-03 17:13

时钟纠正比较简单,下面一个图就能说清楚。 首先为什么要使用时钟纠正,是因为CDR恢复的用户时钟user_clk和硬核时钟XCLK虽然频率一样,但是会有略微的不同,正是这

2018-06-26 09:18

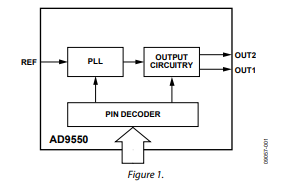

AD9550是一款基于锁相环(PLL)的时钟转换器,针对有线通信和基站应用的需求而设计。它采用整数N分频PLL来满足相关的频率转换要求。REF输入端支持单端输入参考信号

2025-04-10 15:43

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

2017-02-09 12:54

Xilinx为所有设备都提供了standalone模式的驱动程序。Xilinx SDK会根据硬件系统的配置情况,将使用的设备的驱动加入到创建的BSP工程中。Xilinx设备的驱动程序的存放路径是安装

2017-11-18 10:51

除了丰富的时钟网络以外,Xilinx还提供了强大的时钟管理功能,提供更多更灵活的时钟。Xilinx在

2017-02-11 09:14