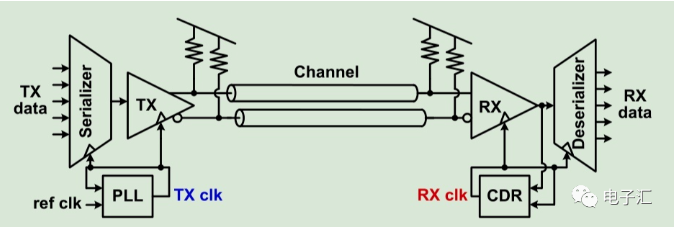

对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个

2017-11-16 01:01

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.

2017-11-22 07:09

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通

2023-08-31 10:44

第一级,即M23级,将DS3信号解复用为7个独立的DS2信号。不是恢复单个DS2时钟,而是创建DS2使能。七个DS2使能中的每一个都处于活动状态,每个DS3帧的DS3时钟

2023-01-13 10:50

在当今高速发展的通信技术中,时钟恢复已成为实现高速串行数据传输的关键。这项技术广泛应用于以太网、PCI Express、Aurora等通信协议中,成为这些系统达到高带宽传输不可或缺的一部分。本文将

2024-09-10 10:38

DS3112 DS3/E3多路复用成帧器具有三种多路复用工作模式。本应用笔记描述了器件如何从三种工作模式下的高速多路复用信号中恢复低速

2023-02-07 11:36

。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时

2023-07-24 11:07

1. Xilinx 时钟资源 xilinx 时钟资源分为两种:全局时钟和第二全局

2017-02-09 08:43

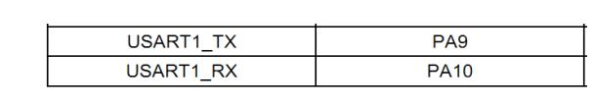

STM32的AFIO时钟真的是在开启引脚复用功能的时候开启吗?其实并不是~

2020-04-04 17:22