本文介绍的基于Wishbone总线的UART IP核的设计方法,通过验证表明了各项功能达到预期要求,为IP核接口的标准化设计提供了依据。此外,该IP核代码全部采用模块化的Verilog-HDL语言编写,

2011-06-10 11:47

Am29LV160D是一种仅需采用3.0V电源进行读写的闪存。该器件提供了70ns、90ns、120ns读取时间,无需高速微处理器插入等待状态进行速度匹配。为了消除总线竞争,芯片引入了片选使能

2018-07-17 15:58

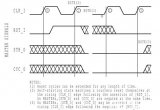

在时钟上升沿1,主设备将DAT_I()采样完成整个突发读操作,同时主设备将新地址信号放到地址总线ADR_O()上,将新数据信号放到数据总线DAT_O()上,将WE_O置为高表示写操作,CTI_O

2018-07-26 09:01

在以上介绍的三种总线中,CoreConnect虽免费不过需要IBM 公司许可,ARM 没有明确的正式说法,可能也会免费,而Wishbone 是绝对免费的。三种总线都是同步的总线

2018-08-11 09:14

随着微电子设计技术与工艺的迅速发展,数字集成电路逐步发展到专用集成电路(ASIC),其中超大规模、高速、低功耗的新型FPGA的出现,降低了产品的成本,提高了系统的可靠性。同时,

2012-05-23 11:14

规则3.20:以下主机信号必须在RST_I置位(变为1)后的第一个时钟上升沿复位(变为0),直到RST_I被复位(变为0)后的第一个时钟上升沿到来:STB_O,CYC_O。所有的其他主机此时不能操作这些信号,以响应复位周期。RST_I被复位(变为0)后的第一个时钟上升沿到来后,主机接口的STB_O和CYC_O信号可以被立即置位(变为1)。

2018-07-11 09:07

在时钟上升沿4,从设备检测到主设备的写操作,将DAT_I()采样。同时从设备发现没有足够的空间存储数据或者由于其他原因不能及时接收新的数据,于是将ACK_O置低插入等待周期。主设备检测到ACK_I为高,于是发起第三次操作,更新DAT_O()。

2018-07-27 09:02

所谓的小端模式(Little-endian),是指数据的高字节保存在内存的高地址中,而数据的低字节保存在内存的低地址中,这种存储模式将地址的高低和数据位权有效地结合起来,高地址部分权值高,低地址部分权值低,和我们的逻辑方法一致。

2018-07-22 10:14

在图25的上升沿1,主设备发起操作,在上升沿2,从设备将ACK_O置高,在上升沿3,从设备知道主设备将发起新的操作,于是将ACK_O继续置高。因此, 3个时钟周期就完成了2次操作,而不是原来大的4个时钟周期,于是吞吐量提高了25%。一般的,改进后,N次操作需要N+1个时钟周期,而不是2N个时钟周期,吞吐量改善为(N-1)/N%。

2018-07-24 09:08

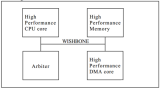

摘要:基于IP可重用的设计方法,利用WISHBONE总线协议,把两个已成功开发出的具有自主知识产权的THUMP内核在一个芯片上,实现了片上多处理器FPGA。开发重点是实

2009-06-20 15:29