当在输入和输出中遇到换行符时,标准I/O库执行I/O操作。这允许我们一次输出一个字符,但只有在写了一行之后才进行实际I/O操作。

2020-07-01 17:17

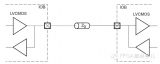

你好Xilinx收发器使用CML IOSTANDARD。在xilinx 7系列示例设计中,有固定的GTREFCLK位置,但其他引脚未配置(txdata / rxdata)在下面的I / O表中,txdata和rxdata引脚未配置CML I / O

2020-08-13 10:10

有份作业要求查I/O标准有哪些,及其电平指标和使用场合,百度谷歌不到详细介绍的,有可以推荐的地址或是书本么?感激不尽哈,或者直接回我下,拜托了

2013-09-13 20:58

面对似乎层出不穷的新 I/O 标准,目前嵌入式系统设计人员继续依靠 FPGA 来部署系统日益重要的外部 I/O 接口,这点丝毫不足为奇。FPGA 可提供大量可配置的 I/O

2010-11-02 09:50

I/O接口标准1.单端信号接口标准LVTTL和LVCMOS(JESD8-5,JESD8-B)SSTL(JESD8-8,JESD8-9B,JESD8-15)HSTL(JESD8-6)LVTTL

2021-11-17 06:38

了解设计人员在使用Zynq-7000 All Programmable SoC器件时可用的不同I / O,从标准I / O到串行收发器以及模拟输入。

2018-11-26 06:36

我想使用外部1K Hz时钟或写入遇到代码将时钟分配到K Hz电平,它会起作用吗? 第二个问题是如何定义I / O类型,我想使用单个lvcmos3.3V作为I / O标准。我应该在哪里定义I /

2020-04-29 09:22

o型圈沟槽尺寸标准O型圈密封为什么泄漏?当O型圈的密封密接触面间发生轻微渗漏,油液随后流出,会是什么原因?O型圈材料结构

2018-12-05 10:32

本章前面几节所述的文件及I/O读写都是基于文件描述符的。这些都是基本的I/O控制,是不带缓存的。而本节所要讨论的I/O操作都是基于流缓冲的,它是符合ANSI C的标准I

2017-10-18 15:45

Xilinx FPGA的I/O兼容多种电平标准,包括LVTTL、LVCMOS、LVDS、LVPECL等,下面对各类电平标准做简要介绍。 一、LVTTL(LowVoltage

2017-02-08 03:42