本篇主要针对Zynq UltraScale + MPSoC的DDR接口,从硬件设计的角度进行详细介绍,最后展示一下小编之前自己设计的基于ZU+的外挂8颗DDR4的设计。 目前比较常用的

2021-09-16 10:17

《基于“矿板”低成本学习Zynq系列》之六-DDR测试

2023-07-19 19:19

设计。第二部分是PLDMA的源码部分。 首先定制zynq核,ddr与uart的配置省略,前面已经写过很多。 配置PL PS互连配置 配置PL IO的工作时钟,FCLK_CLK0对应AXI APB总线工作

2017-11-21 10:42

在Vivado下完之前,先把Zynq的软件编译环境安装好,可以用来重新编译基于Zynq的Linux系统,同时能写基于Zynq的C程序(其实

2017-02-10 15:54

首先新建ddr的IP,具体每个参数的含义,可以参考之前写的

2022-08-17 09:39

麻烦,灵活性也比较差,本节课程讲解如何直接通过AXI总线来读写PS端ddr的数据,这里面涉及到AXI4协议,vivado的FPGA调试等。

2021-01-30 09:54

Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上与

2022-02-08 15:51

最近项目需要用到DDR,于是在网上找相关资料,发现网上关于Xilinx DDR的资料不多,而且比较老,官方文档又是纯英文,且超级长。所以笔者写了这篇文章,为像笔者一样的初学者介绍一下DDR的使用。 在此不介绍

2018-06-28 11:30

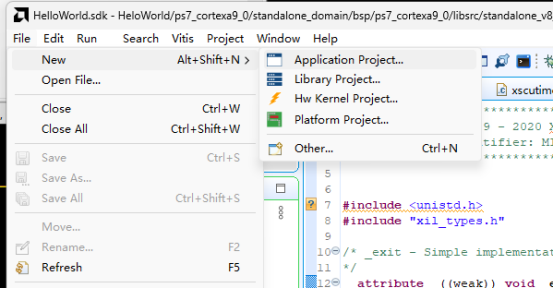

本教程介绍了如何使用μC/ OS BSP建立在ZYNQ基本应用程序®使用Vivado -7000 ™ IDE和赛灵思® SDK。在本教程中,您将使用Vivado IP集成器配置

2017-11-17 15:06

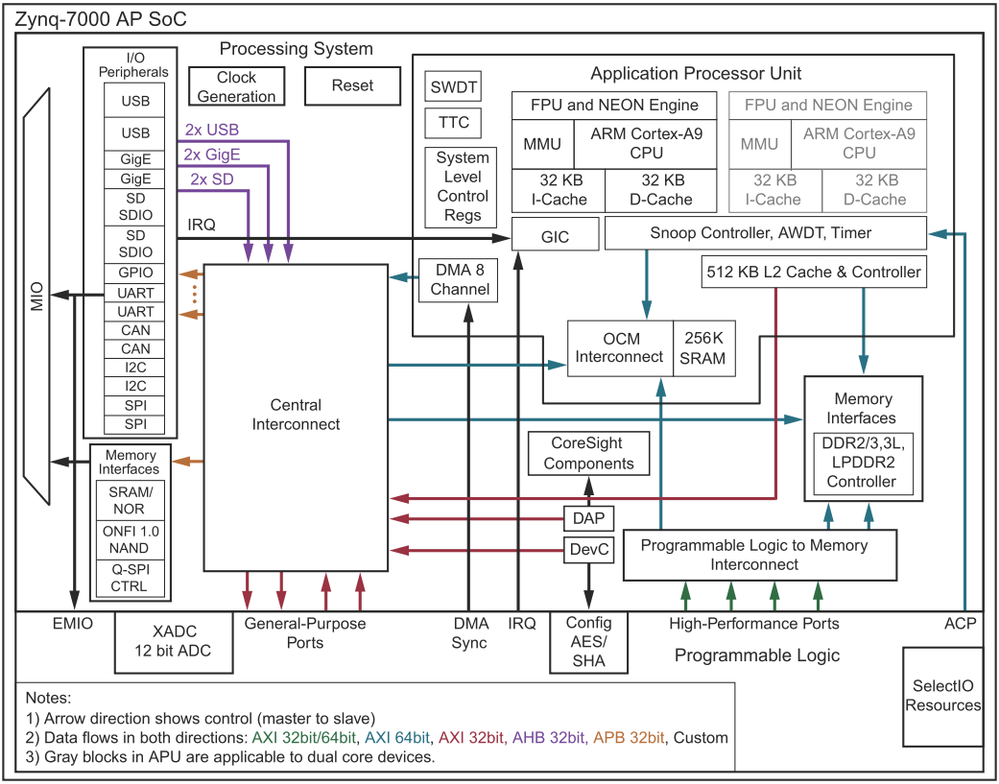

ZYNQ概述 ZYNQ内部包含PS和PL两部分,PS中包含以下4个主要功能模块: Application processor unit (APU) Memory interfaces I/O

2020-11-03 12:33