这个设计是根据avnet的PL dma带宽测试程序修改过来的,只使用了其中的HP0一个PLDMA。分为两个部分进行设计,第一部分是关于vivado中的block design部分,就是通过ip进行

2017-11-21 10:42

通过前面的PL DMA设计,在SDK中运行,很正常的没有运行起来(block design与source desing都是自己手敲,明显的错误已经改正,能够生成bit文件启动SDK调试)。 首先在PL部分调试,作为PL DMA的控制APB总线,将其设置为Mark Debug,如下图所示。综合完成,不进行implemention,在综合菜单下面找到“Set Up Debug”,进行ILA配置。

2017-11-28 15:46

在Vivado下完之前,先把Zynq的软件编译环境安装好,可以用来重新编译基于Zynq的Linux系统,同时能写基于Zynq的C程序(其实

2017-02-10 15:54

本教程介绍了如何使用μC/ OS BSP建立在ZYNQ基本应用程序®使用Vivado -7000 ™ IDE和赛灵思® SDK。在本教程中,您将使用Vivado IP集成器配置

2017-11-17 15:06

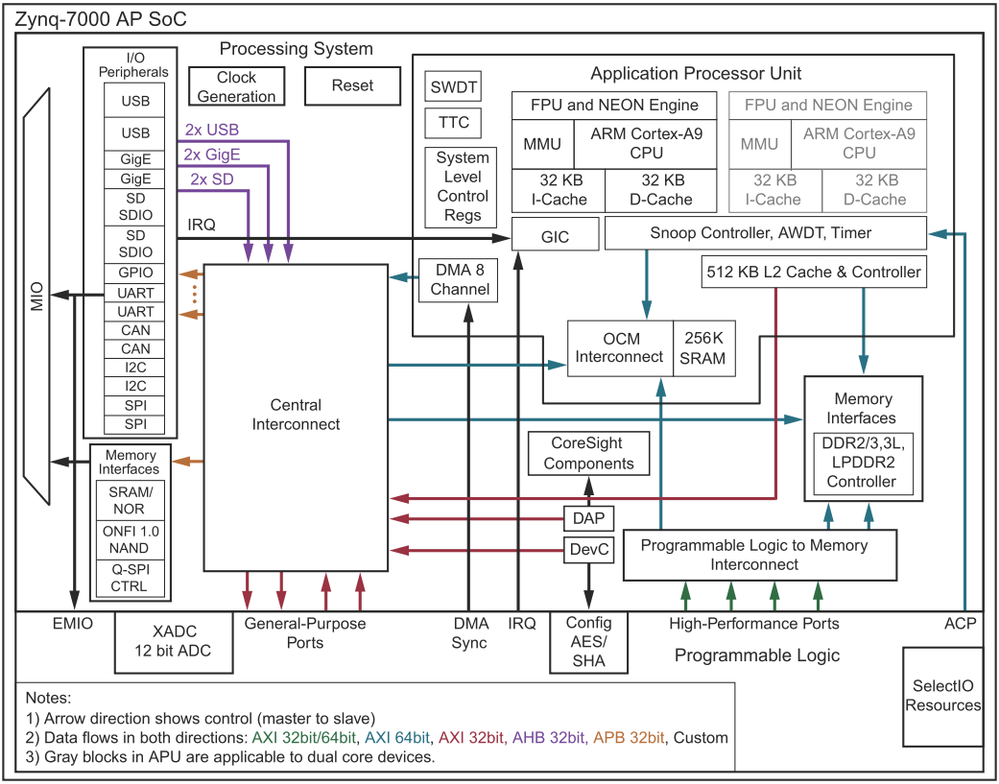

ZYNQ概述 ZYNQ内部包含PS和PL两部分,PS中包含以下4个主要功能模块: Application processor unit (APU) Memory interfaces I/O

2020-11-03 12:33

新的器件支持包括:Kintex®UltraScale+™,Zynq®UltraScale+ MPSoC和所有Vivado HLx版本的单核Zynq-7000S All Programmable SoC器件,包括Web

2018-11-20 06:50

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38

Step3: 按照“Vivado中进行ZYNQ硬件部分设计”中介绍的,直到在SDK中编写C代码步骤。需要使用UART进行通行,分为通过UART向外发送数据和通过UART接收数据。

2023-09-23 09:25

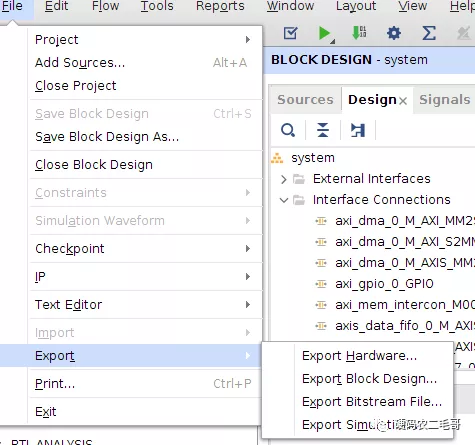

在Zynq开发时,在Vivado中新建Zynq硬件平台,加入DMA、AXI接口模块,在进行构建软件系统之前,通常需要对硬件平台进行验证,检测模块新建过程中是否存在问题。下面对这一过程进行简单介绍。

2022-02-16 16:21

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23