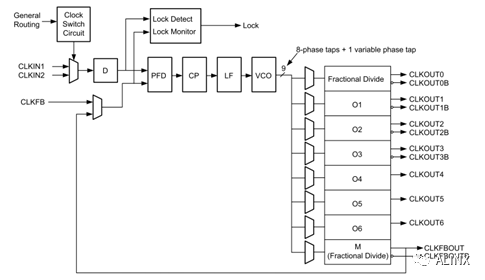

,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2022-02-08 15:13

Vivado 的XDC设置输出延时 Vivado 的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125

2021-06-09 17:28

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

2018-12-22 15:14

PLL对于VCO有什么要求?如何设计VCO输出功率分配器? PLL对于VCO的要求: 1. 频率稳定性:VCO的输出频率需要具有较高的稳定性和准确度。对于

2023-10-30 10:46

符。 Vivado Synthesis Hangs/StopsVivado在综合时,如果显示一直在运转,但不再输出任何log信息时,检查一下工程路径是否包含了特殊字符“”。因为“”字符在Tcl脚本里是变量置换

2021-09-12 15:15

模拟PLL,模拟PLL是什么意思 所谓模拟PLL,就是说数字PLL中的各个模块的实现都是以模拟器件来实现的,是一个模拟

2010-03-23 10:52

数字PLL,什么是数字PLL 数字PLL PLL的概念 我们所说的PLL,其实就是锁相环路,简称为锁相环。许多

2010-03-23 10:50

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

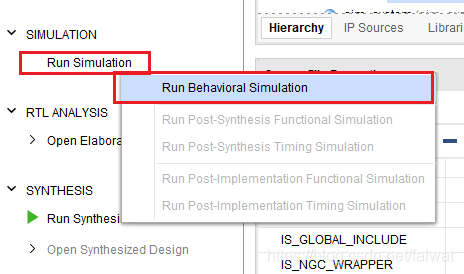

本文介绍如何在教程(三)基础上, 关联ELF输出文件并使用vivado对系统进行行为仿真。

2022-02-08 11:18

PLL锁相环版图设计时应注意以下几点:1)确定PLL的频率范围;2)确定PLL的控制电路;3)确定PLL的调节电路;4)确定PL

2023-02-14 15:42