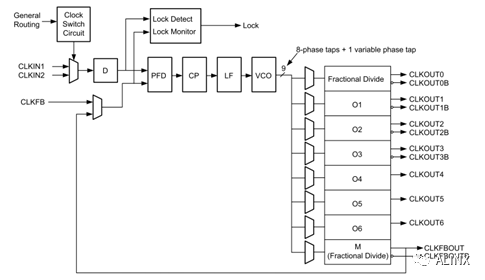

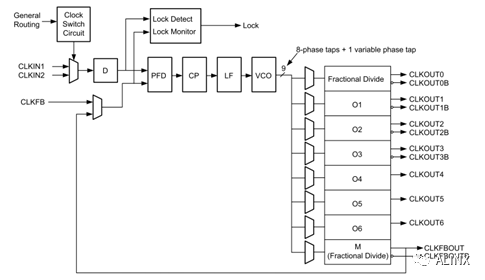

,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2022-02-08 15:13

Vivado 的XDC设置输出延时 Vivado 的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125

2021-06-09 17:28

在做PLL时,输入时钟是50MHZ,希望经过PLL后,输出100MHZ。PLL只有input_clock,areset,c0三个引脚。但是实际上并没有

2014-12-01 09:28

AD9957上电复位后,sync_clk和pdclk均有输出,但使用内部pll后sync_clk有输出而pdclk无输出

2018-09-14 14:14

采用AUX_IN输入25MHz时钟,外部配置引脚如图均设为高电平(经测量确为高电平),芯片寄存器为默认,希望能实现芯片手册示例中的输出(156.25MHz和125MHz等输出)。 经测量芯片供电正常,输入时钟正确给入,但都

2024-11-08 07:07

,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2021-01-29 09:30

本人安装的是Quartus17.0-Lite(配套Modelsim-Altera)添加PLL的IP核,仿真的时候c0输出高阻,locked一直输出低;选用:Cyclone10

2017-11-05 11:59

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

2018-12-22 15:14

电子发烧友网站提供《STM32 F407无传感器控制PLL.zip》资料免费下载

2024-12-19 14:10

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04