前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案

2022-08-29 14:41

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26

LUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!

2022-09-09 09:09

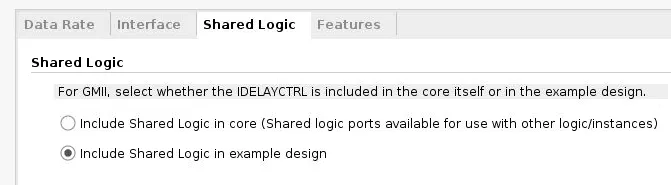

在很多Vivado的高速接口的IP中,比如Ethernet、PCIe、SRIO的设置中,都会有个Shared Logic的页面。可能很多同学并没有很关注这个页面,直接默认设置就完事了。但其实这个页面的内容也是非常有用的,我们可以看到页面中有两个选择:

2022-08-02 09:03

在某些情况下,通过嗅探 AXI 接口来分析其中正在发生的传输事务是很有用的。在本文中,我将为大家演示如何创建基本 AXI4-Lite Sniffer IP 以对特定地址上正在发生的读写传输事务进行计数。

2022-07-08 09:35

Architectural Configuration选择为并行模式,具有单周期数据吞吐量和较大的硅面积。具有并行结构配置的CORDIC核使用移位相加子级数组并行实现这些移位相加操作。该并形电路的实现规模与(内部精度 * 迭代次数)成正比。

2025-05-03 18:16

这篇文章在开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE) 的基础上撰写,但使用的是 AMD Vitis Unified IDE,而不是之前传统版本的 Vitis HLS。

2025-06-20 10:06

最近我们分享了开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE)和开发者分享|AMD Vitis HLS 系列 2:AMD

2025-07-02 10:55

在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之后的设计中继续使用此

2022-04-21 08:58

本教程介绍了如何使用μC/ OS BSP建立在ZYNQ基本应用程序®使用Vivado -7000 ™ IDE和赛灵思® SDK。在本教程中,您将使用Vivado IP集成器配置ZYNQ处理器系统以及

2017-11-17 15:06