在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之后的设计中继续使用此

2022-04-21 08:58

testbench来验证设计。 Integrate带有Xilinx IP Block的 HLS IP 这里展示了在IP Integrator中,如何将两个HLS IP

2017-02-07 17:59

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26

前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案

2022-08-29 14:41

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

2018-12-22 15:14

在给别人用自己的工程时可以封装IP,Vivado用封装IP的工具,可以得到像xilinx的ip一样的可以配置参数的IP核

2018-06-26 11:33

在Vivado下,有两种方式管理IP。一种是创建FPGA工程之后,在当前工程中选中IP Catalog,生成所需IP,这时相应的

2017-11-18 04:22

以Xilinx Vivado设计套件中提供的FFT IP为例,简要说明如何进行FFT IP配置和设计。

2022-07-22 10:21

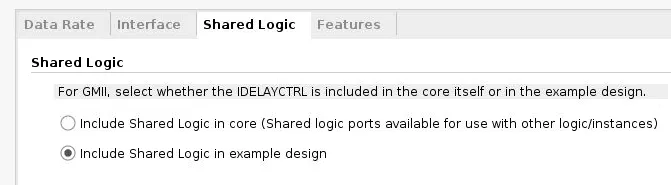

在很多Vivado的高速接口的IP中,比如Ethernet、PCIe、SRIO的设置中,都会有个Shared Logic的页面。可能很多同学并没有很关注这个页面,直接默认设置就完事了。但其实这个页面的内容也是非常有用的,我们可以看到页面中有两个选择:

2022-08-02 09:03

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado

2022-08-02 10:10