DRP时钟为60位RX bufferRXUSRCLK源是RXOUTCLKno逗号检测工具是vivado,版本是2013-03在modelsim仿真中,我发现GTX rx cdrlock无法锁定,它总是每6-7 clk_135m周期无效。

2020-07-28 10:40

本文主要介绍Vivado布线参数设置,基本设置方式和vivado综合参数设置基本一致,将详细说明如何

2023-05-16 16:40

如果你正在使用Vivado开发套件进行设计,你会发现综合设置中提供了许多综合选项。这些选项对综合结果有着潜在的影响,而且能够提升设计效率。为了更好地利用这些资源,需要仔细研究每一个选项的功能。本文将要介绍一下Vivado

2023-05-16 16:45

从Vivado开始,配置GTX的时候,多了一个SATA协议支持,但有些小地方还需要自己另外设置。整理了一下,分享给大家。 首先打开Transceivers wizard: 打开页签,线速率和参考时钟

2019-10-06 20:56

Vivado 的XDC设置输出延时 Vivado 的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125M驱动,伴随时钟是由125M经过Pll相位移动-

2021-06-09 17:28

你好,我正在使用以下工具:Vivado 2015.4questasim64_10.4c我用这个命令编译了模拟库:compile_simlib -directory C:/Xilinx/Vivado

2020-07-31 11:27

我用k7 325t配置一个显示端口GTX rx,我用一个黄金显示端口tx发送数据,我发现GTX rx cdrlock每1秒或2秒为0。GTX的哪个设置会影响rx cdr

2020-07-20 10:48

你好当我将7系列收发器向导用于Kintex-7设备(XC7K70T)时,我无法将GTX速率设置为高于6.6 Gbps的值。 Kintex-7 GTX应该以11.3 Gbps的速度运行,但似乎只适用于

2019-03-06 09:49

测试(路径①),数据流仅通过近端GTX的PCS部分,可用于验证近端GTX中PCS收发双向的设置;近端PMA环回测试(路径②,数据流通过近端GTX的PCS、PMA,可用于

2023-06-21 11:23

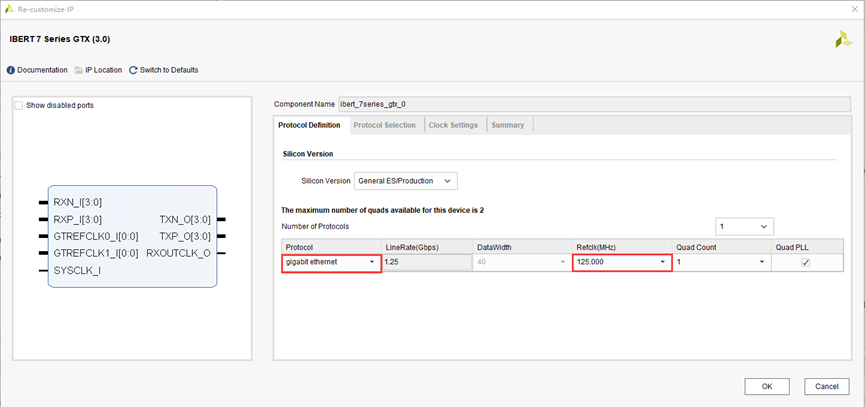

本文介绍一个FPGA开源项目:基于IBERT的GTX数据传输测试。IBERT是指误码率测试,在Vivado软件中,IBERT 7 Series GTX IP核可用于对 Xilinx FPGA芯片

2023-08-31 11:45