在编写Verilog代码时最痛苦的事情便是例化模块时端口的连接,这时候的你我便成了连线工程师,本节就在SpinalHDL中如何像软件调用方法那样优雅地例

2021-06-16 17:19

习惯了写Verilog的小伙伴们在做大型工程时是否有遇到过连续数天时间化身“连线工程师”去例化模块、为端口赋值连接的场景(关键是这些工作量老板他也不认)。尽管在SystemVerilog中提供了

2022-06-13 10:01

首先,什么是XPM?可能很多人没听过也没用过,它的全称是Xilinx Parameterized Macros,也就是Xilinx的参数化的宏,跟原语的例化和使用方式一样。可以在

2020-10-30 15:39

的例化(或说是调用)。在一个FPGA项目工程中,其输入、输出端口命名通常在设计前期就已确定下来,但会存在一些中间变量,一个工程可能会让不同的工程师在不同的时间段内共同完成,不同的人对于这些变量的命名会有所不同,故

2024-12-17 11:29

模块间的例化(或说是调用)。在一个FPGA项目工程中,其输入、输出端口命名通常在设计前期就已确定下来,但会存在一些中间变量,一个工程可能会让不同的工程师在不同的时间段内共同完成,不同的人对于这些变量的命名会有所不同,

2022-12-12 09:50

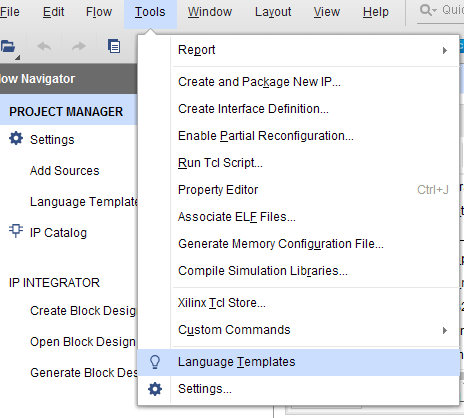

其实Tcl在Vivado中还有很多延展应用,接下来我们就来讨论如何利用Tcl语言的灵活性和可扩展性,在Vivado中实现定制化的FPGA设计流程。 基本的FPGA设计实现流程 FPGA的设计流程简单来讲,就是从源代码

2017-11-18 01:48

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado

2022-08-02 10:10

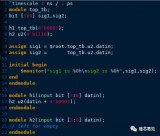

我们以8-bit 的LFSR(线性反馈移位寄存器)做一个流水灯为例,介绍Vivado的基本使用。

2018-09-25 16:16

本文讲述了如何使用 One Spin 检查 AMD Vivado Design Suite Synth 的结果(以 Vivado 2024.2 为例)。

2025-05-19 14:22

示例中,在顶层top_tb中例化了两个module(h1和h2),例化名分别是top_tb和u2,其中h1中又例化了h2,也就是h2在顶层top_tb和h1中分别进行了例

2023-04-28 10:28