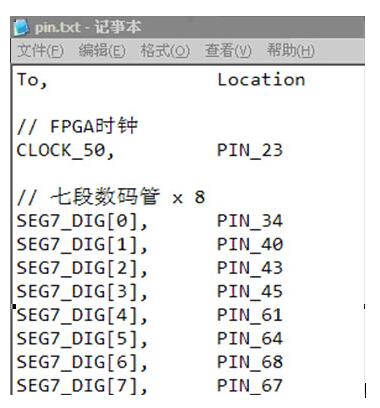

将Quartus II中FPGA管脚的分配及保存方法做一个汇总。本文首先介绍了FPGA 的管脚分配方法,其次介绍了Quartus II自动添加

2018-05-16 11:44

本文通过一个简单的例子,介绍Vivado 下的仿真过程。主要参考了miz702的教程,同时也参考了Xilinx的ug937, xapp199.。

2018-11-10 10:53

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从

2017-11-25 07:38

设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚

2017-02-11 03:48

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,使用Vivado开发软件下板验证教程。话不多说,上货。

2023-03-08 14:21

在Vivado中新建IO Planning工程来初步引脚分配,这样会大大提高开发效率 在这里,你可以选择最右侧的开发板型号,也可以选择Part,具体的FPGA的型号,选择完后,我们可以很清晰的看到该型号的资源列表:包括IO数、可用的IO数、内部BRAM大小、时钟

2018-10-22 17:12

在ISE下,对综合后的网表进行编辑几乎是不可能的事情,但在Vivado下成为可能。Vivado对Tcl的支持,使得Tcl脚本在FPGA设计中有了用武之地。本文通过一个实例演示如何在

2017-11-18 03:16

Spartan-6系列具有低成本、省空间的封装形式,能使用户引脚密度最大化。所有Spartan-6 LX器件之间的引脚分配是兼容的,所有Spartan-6 LXT器件之间的引脚分配是兼容的,但是Spartan-6 LX和Spartan-6 LXT器件之间的引脚

2018-07-01 10:48

在Vivado Design Suite中,Vivado综合能够合成多种类型的属性。在大多数情况下,这些属性具有相同的语法和相同的行为。

2019-05-02 10:13

在使用JTAG仿真器在vivado环境下抓信号时,报如下错误:

2023-11-14 10:37